# Embedded multiprocessor architectures for automative driver assistance systems

Jehangir Khan

#### ▶ To cite this version:

Jehangir Khan. Embedded multiprocessor architectures for automative driver assistance systems. Embedded Systems. Université de Valenciennes et du Hainaut Cambraisis, 2009. English. NNT: 2009 VALE 0034. tel-03065222

## HAL Id: tel-03065222 https://uphf.hal.science/tel-03065222v1

Submitted on 14 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Université de Valenciennes et du Hainaut-Cambrésis

Numéro d'ordre: 09/43

# **Embedded Multiprocessor Architectures for Automotive Driver Assistance Systems**

## Dissertation

Presented and defended on:

26<sup>th</sup> November 2009

For obtaining

## Doctorate Degree

At the Université de Valenciennes et du Hainaut-Cambrésis, France

Specialty: Automatique et Informatique des Systèmes Industriels et Humains

Domain: Embedded Systems

by

Jehangir KHAN

Referees:

Mladen Berekovic

Professeur Faculty of Electrical Engineering,

Technique Univeritat (TU) Braunschweig (Allemagne).

Olivier Sentievs

Professeur INRIA Rennes - Bretagne Atlantique.

Examiners:

Mazen Saghir

Professeur University of Texas A&M à Doha (Qatar).

Amer Baghdadi

Maître de conférences, Télécom Bretagne (ex ENST) Brest.

Supervisor:

Pr. Smail NIAR

LAMIH, Université de Valenciennes

Co-supervisor:

Pr. Atika MENHAJ-RIVENQ

IEMN, Université de Valenciennes

# Acknowledgements

## **Summary**

Automotive crashes are responsible for the highest number of accidental deaths all over the world. Researchers, automotive manufacturers and government authorities around the world are continuously looking for solutions to this problem. Research has shown that half of the accidents can be avoided if a driver is alerted to an impending collision a fraction of a second in advance. A mechanism for warning the driver of an approaching danger is called a Driver Assistance System (DAS).

Accident statistics show that a great majority of the vehicle crashes result from front-end collisions. Hence minimizing frontal collisions would significantly decrease road accidents. To predict a front-end collision sufficiently in advance, the obstacle must be detected from a distance. Moreover, for the DAS to be really effective, an imminent collision must be sensed in all circumstances, especially in poor weather where the DAS is needed most. A radar sensor fulfills both the prerequisites of long range obstacle detection and all-weather operation. However, only detecting obstacles can be useful to a certain extent. To establish whether an obstacle is on a collision course with the host vehicle, its trajectory must be foreseen before it comes close to the host vehicle. Determining the trajectory of a moving object requires its dynamic behavior to be monitored over a period of time. In a real traffic scenario more than one obstacle can pose danger to the host vehicle, hence trajectories of multiple objects have to be monitored simultaneously. An apparatus which is capable of performing such functions is called a Multiple Target Tracking (MTT) system.

In this thesis we propose a DAS using the principles of Multiple Target Tracking to monitor the dynamics of obstacles hundreds of meters ahead and to avoid a collision of the host vehicle with them. While theoretically such a system offers one of the best answers to the road accident problem, its practical implementation is not a trivial task. It involves complex computations and consequently, needs a long processing time. However, to alert a driver to an approaching danger in real time, the computations must be performed very rapidly. We use multiple processors in our system to share the computation load and thereby reduce the processing time. Multiple processors running in parallel not only speed up the computation but also address the power consumption issues of the embedded systems.

We use FPGA (Field Programmable Gate Array) as the implementation platform for our multiprocessor system. FPGAs offer the flexibility needed for the ever evolving embedded systems and they are very cost effective. A multiprocessor system implemented in an FPGA makes its architecture flexible and reconfigurable while the processors can be reprogrammed

when needed. Thus FPGA based multiprocessor systems guarantee flexibility in hardware as well as in software therefore they scale very easily. We optimize the system architecture to minimize its hardware size while still meeting the realtime deadlines of the application. Minimized hardware not only leads to reducing energy consumption of the system but also enables us to fit the system in a smaller FPGA which plays an important role in reducing the cost of the system.

## Résumé

Les accidents de véhicules automobiles sont responsables du plus grand nombre de décès dans le monde. Les chercheurs, les constructeurs automobiles et les autorités gouvernementales internationaux sont continuellement à la recherche de solutions pour résoudre ce problème. La recherche a montré que la moitié des accidents peut être évitée si le conducteur est alerté d'une collision imminente une fraction de seconde à l'avance. Un mécanisme d'alerte d'un danger proche est appelé Driver Assistance Systems (DAS).

Les statistiques montrent qu'une grande majorité des accidents de véhicules se passent à la suite d'une collision frontale. Minimiser les collisions frontales devrait donc diminuer considérablement les accidents de la route. Pour prévoir une collision frontale suffisamment à l'avance, l'obstacle doit être détecté à distance. En outre, pour que le DAS soit réellement efficace, une collision imminente doit être prévue en tenant compte de toutes les circonstances : par exemple plus il fait mauvais, plus le DAS est nécessaire. Un capteur radar remplit les conditions préalables de détection d'obstacles à longue portée en tenant compte des conditions météorologiques. Toutefois, seule la détection des obstacles peut être utile dans une certaine mesure. Pour déterminer si un obstacle se trouve sur une trajectoire de collision avec le véhicule d'accueil, sa trajectoire doit être prévue avant qu'il n'arrive près du véhicule d'accueil. La détermination de la trajectoire d'un objet en mouvement exige que son comportement dynamique soit suivi sur une période de temps. Dans un scénario de trafic réel, plus d'un obstacle peut être considéré comme un danger pour le véhicule d'accueil, c'est pourquoi les trajectoires d'objets multiples doivent être surveillées simultanément. Un appareil capable d'exercer de telles fonctions est appelé un système de suivi d'obstacles multiples ou Multiple Target Tracking (MTT).

Dans cette thèse nous proposons un DAS en utilisant les principes du MTT pour suivre la dynamique d'obstacles situés à plus d'une centaine de mètres et pour éviter une collision du

véhicule hôte avec ceux-ci. En théorie, un tel système offre une des meilleures réponses au problème des accidents de la route, mais sa mise en œuvre pratique n'est pas une tâche triviale. Elle implique des calculs complexes et, par conséquent, les besoins de traitement prennent du temps. Cependant, pour aviser le conducteur d'un danger imminent en temps réel, les calculs doivent être effectués très rapidement. Nous utilisons plusieurs processeurs dans notre système afin de partager la charge de calcul et de réduire ainsi le temps de traitement. Les processeurs multiples fonctionnant en parallèle permettent non seulement d'accélérer le calcul, mais aussi d'aborder les questions de consommation d'énergie du système embarqué.

Nous utilisons des FPGA (Field Programmable Gate Array) comme plateforme de mise en œuvre de notre système multiprocesseur. Les FPGA offrent la souplesse nécessaire pour les systèmes embarqués en constante évolution et sont très rentables. Un système multiprocesseur réalisé dans un FPGA rend son architecture flexible et reconfigurable tandis que les processeurs peuvent être reprogrammés si nécessaire. Ainsi les systèmes multiprocesseurs à base de FPGA garantissent une souplesse dans le matériel ainsi que dans les logiciels, et par conséquent leur passage à échelle est aisé. Nous optimisons l'architecture du système afin de minimiser la taille du matériel tout en respectant les délais en temps réel de l'application. La minimisation du matériel ne conduit pas seulement à réduire la consommation d'énergie du système, mais nous permet aussi d'adapter le système dans un FPGA plus petit. Cela joue un rôle important dans la réduction du coût du système.

## Scientific output of the work

- 1. Trade-off exploration for target tracking application in a customized multiprocessor Architecture(to appear). Design and Architectures for Signal and Image Processing, Special Issue of the EURASIP Journal of Embedded Systems.

- 2. Radar Based Collision Avoidance System Implementation in a Reconfigurable MPSoC The 9<sup>th</sup> International Conference on ITS Telecommunications, ITST 2009, 20-22 Oct. 2009 Lille France.

- 3. Driver Assistance System Design and its Optimization for FPGA Based MPSoC IEEE Symposium on Application Specific Processors, SASP 2009, July 27-28, 2009 San Francisco, California

- 4. Multiple Target Tracking System Design for Driver Assistance Application.,

Design & Architectures for Signal and Image processing, Brussels, Belgium, November 2008.

- 5. An MPSoC Architecture for the Multiple Target Tracking Application in Driver Assistant System. 19th IEEE International Conference Application-specific Systems, Architectures and Processors (ASAP) Leuven, Belgium, July 2008.

- 6. A Multiple Target Tracking SoC for Transport Security. Colloque du GDR SOC SIP, Paris, June 2007.

- 7. Système d'aide à la conduite par l'utilisation du suivi d'obstacles multiples sur architecture multiprocesseurs reconfigurable. Séminaire Systèmes Embarqués : Sécurité, Confort, Aide à la conduite, ESIEE Amiens, May 2008

- 8. An Efficient Digital Correlator Architecture for an Anti-Collision Radar System. *ACES* 2006, Edegem Belgium, October 2006.

- Resource Optimization in Ati-collision Correlation Radar. Mémoire de DEA, UVHC, France, Septembre 2006.

- 10. A low Speed Digital Correlator Architecture Optimized For Resource Savings. Reconfigurable Communication-centric SoCs (RECOSoC), Montpellier France, July 2006.

## **Table of Contents**

| ACKN   | OWLEDGEMENTS                                | 111 |

|--------|---------------------------------------------|-----|

| SUMN   | MARY                                        | v   |

| RÉSUN  | MÉ                                          | VI  |

| SCIEN. | TIFIC OUTPUT OF THE WORK                    | VII |

| TABLE  | OF CONTENTS                                 | XI  |

| LIST O | PF FIGURES                                  | xv  |

| INTRO  | DDUCTION                                    | 1   |

| 1.     | GENERAL INTRODUCTION                        | 1   |

| 2.     | PROBLEM DIAGNOSIS AND OUR PROPOSED SOLUTION | 3   |

| 3.     | PLAN OF THE DOCUMENT                        | 5   |

| RELAT  | FED WORK AND MOTIVATION                     | 9   |

| 1.     | Introduction                                | 9   |

| 2.     | DRIVER ASSISTANCE SYSTEMS                   | 10  |

| 2.1.   | THE INTERSAFE PROJECT                       | 10  |

| 2.2.   | HONDA HIDS                                  | 11  |

| 2.3.   | SEAT ADAS                                   | 11  |

| 2.4.   | THE SARI / RADARR PROJECT                   | 12  |

| 2.5.   | THE CHAMELEON PROJECT                       | 12  |

| 2.6.   | OTHER LESS KNOWN DAS'S                      | 13  |

| 2.7.   | CRITIQUE OF THE PRESENTED DASS              | 13  |

| 2.8.   | Our Proposal                                | 14  |

| 3.     | WORK RELATED TO MULTIPLE TARGET TRACKING    | 15  |

| 4.     | PLATFORMS FOR AUTOMOTIVE APPLICATIONS       | 16  |

| 4.1.   | IMAPCAR                                     | 17  |

| 4.2.   | EyeQ2                                       | 18  |

| 4.3.                                | VIP-II                                                         | . 19                         |

|-------------------------------------|----------------------------------------------------------------|------------------------------|

| 4.4.                                | MPC5561 MICROCONTROLLER                                        | . 20                         |

| 4.5.                                | TMS570F                                                        | . 21                         |

| 4.6.                                | Critique                                                       | . 21                         |

| 4.7.                                | OUR PROPOSAL                                                   | . 22                         |

| 5.                                  | MPSoC Architectures for Other Applications                     | . 23                         |

| 5.1.                                | C-5 NP                                                         | . 23                         |

| 5.2.                                | VIPER NEXPERIA                                                 | . 25                         |

| 5.3.                                | OMAP                                                           | . 25                         |

| 5.4.                                | ARM MPCORE                                                     | . 26                         |

| 5.5.                                | THE CELL PROCESSOR                                             | . 27                         |

| 5.6.                                | DISCUSSION AND CRITIQUE                                        | . 28                         |

| 5.7.                                | OUR PROPOSAL                                                   | . 29                         |

| 6.                                  | THE HARDWARE / SOFTWARE CO-DESIGN FLOW                         | . 31                         |

| 7.                                  | CHAPTER SUMMARY                                                | . 32                         |

| MULTII                              | PLE TARGET TRACKING APPLICATION MODELING FOR AUTOMOTIVE SAFETY | 35                           |

| 1.                                  | INTRODUCTION                                                   | . 35                         |

| 2.                                  | MULTIPLE TARGET TRACKING (MTT) APPLICATION                     | . 37                         |

| 2.1.                                | TERMINOLOGY                                                    | . 38                         |

| 2.2.                                | GENERAL PRINCIPLES                                             | . 39                         |

| 2.3.                                | MTT BUILDING BLOCKS                                            | . 42                         |

| 3.                                  | MTT MATHEMATICAL MODELING: OUR APPROACH                        | . 44                         |

| 3.1.                                |                                                                |                              |

|                                     | Process Model                                                  |                              |

| 3.2.                                |                                                                | . 45                         |

| <ul><li>3.2.</li><li>3.3.</li></ul> | Process Model                                                  | . 45<br>. 46                 |

|                                     | PROCESS MODEL                                                  | . 45<br>. 46<br>. 47         |

| 3.3.                                | PROCESS MODEL  MEASUREMENT MODEL  FILTERING AND PREDICTION     | . 45<br>. 46<br>. 47<br>. 51 |

| 3.7.   | ASSIGNMENT SOLVER                              | 59  |

|--------|------------------------------------------------|-----|

| 3.8.   | TRACK MAINTENANCE                              | 66  |

| 4.     | CHAPTER SUMMARY                                | 67  |

| APPLIC | CATION TO ARCHITECTURE MAPPING                 | 71  |

| 1.     | Introduction                                   | 71  |

| 2.     | IMPLEMENTATION CHOICES                         | 72  |

| 3.     | IMPLEMENTATION PLATFORM AND DESIGN ENVIRONMENT | 73  |

| 4.     | THE NIOS II PROCESSOR                          | 76  |

| 5.     | STRUCTURING APPLICATION FOR PARALLEL MAPPING   | 78  |

| 6.     | SYSTEM SOFTWARE                                | 80  |

| 7.     | APPLICATION PROFILING                          | 81  |

| 7.1.   | APPLICATION RUNTIME                            | 82  |

| 7.2.   | MEMORY REQUIREMENTS                            | 85  |

| 8.     | SOFTWARE TO HARDWARE MAPPING                   | 86  |

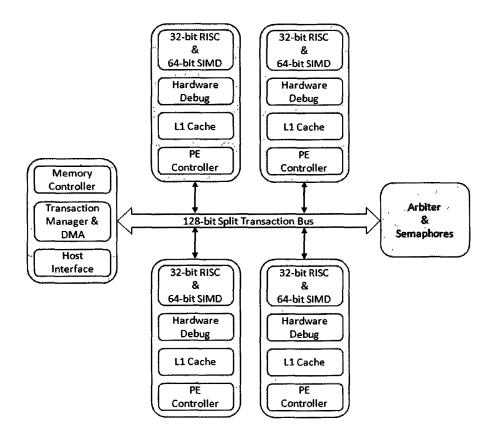

| 9.     | PRELIMINARY SYSTEM ARCHITECTURE                | 89  |

| 10.    | CHAPTER SUMMARY                                | 92  |

| ANALY  | YSIS AND OPTIMIZATION                          | 95  |

| 1.     | Introduction                                   | 95  |

| 2.     | CONSTRAINTS                                    | 96  |

| 3.     | OPTIMIZATION STRATEGIES                        | 98  |

| 3.1.   | CHOICE OF NIOSII IMPLEMENTATION                | 99  |

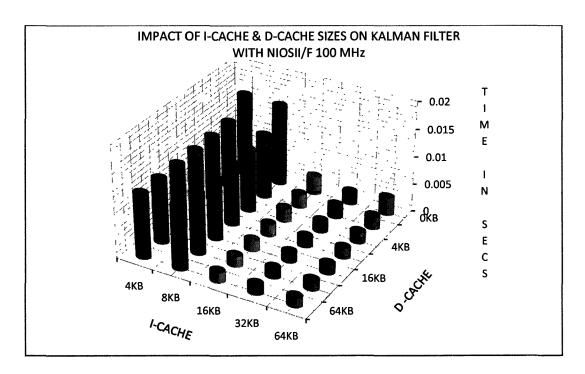

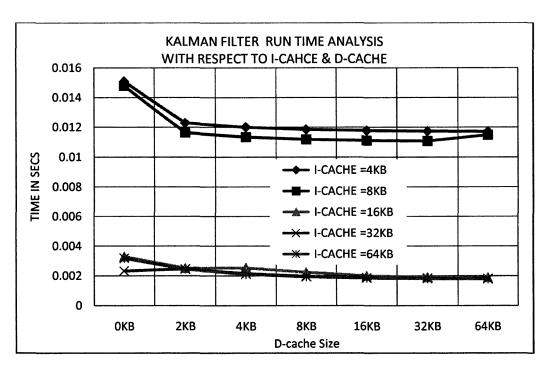

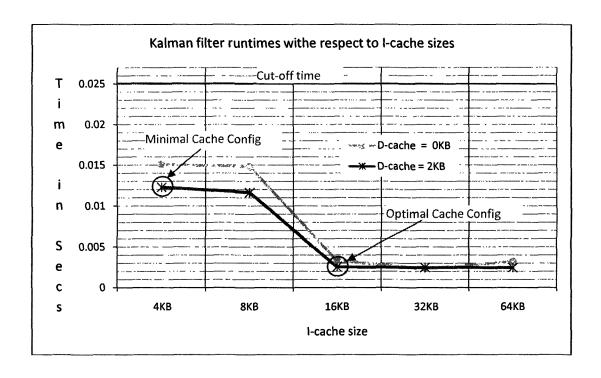

| 3.2.   | I-CACHE & D-CACHE                              | 99  |

| 3.3.   | FLOATING POINT CUSTOM INSTRUCTIONS             | 100 |

| 3.4.   | ON CHIP VS OFF CHIP MEMORY SECTIONS            | 101 |

| 3.5.   | C2H COMPILER                                   | 102 |

| 4.     | KALMAN FILTER OPTIMIZATION                     | 103 |

| 4.2.   | FLOATING POINT CUSTOM INSTRUCTIONS             | 106 |

| 4.3.   | On-Chip Memory                                                  |

|--------|-----------------------------------------------------------------|

| 5.     | GATING MODULE OPTIMIZATION                                      |

| 5.2.   | FLOATING POINT CUSTOM INSTRUCTIONS                              |

| 5.3.   | On-Chip Memory                                                  |

| 6.     | MUNKRES ALGORITHM OPTIMIZATION                                  |

| 6.2.   | FLOATING POINT CUSTOM INSTRUCTIONS                              |

| 6.3.   | MUNKRES ALGORITHM AND MEMORY SECTIONS                           |

| 6.4.   | FLOATING POINT VS INTEGER COST MATRIX FOR MUNKRES ALGORITHM 117 |

| 6.5.   | DISCUSSION                                                      |

| 7.     | TRACK MAINTENANCE                                               |

| 8.     | CHAPTER SUMMARY                                                 |

| SUMN   | IARY AND FUTURE WORK                                            |

| 1.     | SUMMARY ERROR! BOOKMARK NOT DEFINED.                            |

| 2.     | FUTURE WORK ERROR! BOOKMARK NOT DEFINED.                        |

| APPEN  | IDICES                                                          |

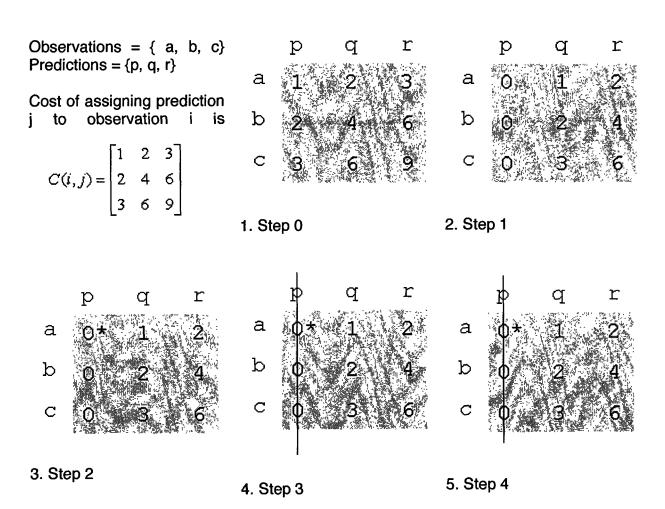

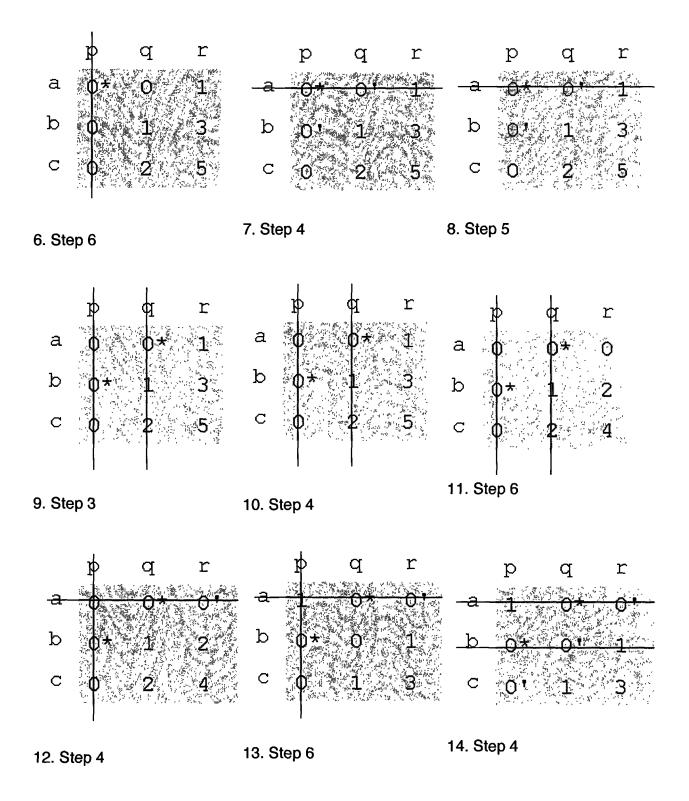

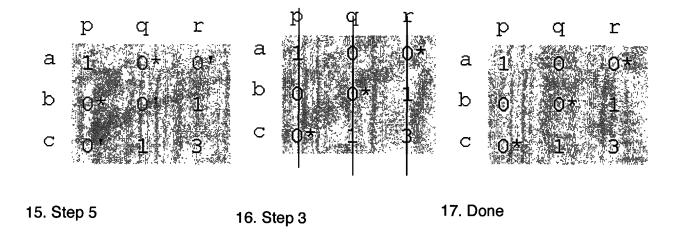

| A.     | AN EXAMPLE ASSIGNMENT PROBLEM SOLVED BY MUNKRES ALGORITHM 131   |

| B.     | SOME MPSOC ARCHITECTURES                                        |

| C.     | NIOS II ARCHITECTURAL DEATAILS                                  |

| BIBLIC | GRAPHY148                                                       |

| THESIS | TITLE ERROR! BOOKMARK NOT DEFINED.                              |

| ABST   | RACT ERROR! BOOKMARK NOT DEFINED.                               |

| TITRE  | DE LA THÈSE ERROR! BOOKMARK NOT DEFINED.                        |

| RESU   | ME ERROR! ROOKMARK NOT DEFINED                                  |

## List of figures

| Figure 1:  | Road Accident Fatalities in Developed Countries Source: (2) |

|------------|-------------------------------------------------------------|

| Figure 2   | : DAS's help reduce Drivers' Mental Stress source (9)       |

| Figure 3:  | Accident Profile of an Automotivesource: (10)               |

| Figure 4:  | A simplified illustration of our proposed DAS5              |

| Figure 5:  | The IMAPCAR Architecture                                    |

| Figure 6:  | The EyeQ2 Architecture                                      |

| Figure 7:  | The VIP-II Architecture                                     |

| Figure 8:  | The MPC5561 Architecture                                    |

| Figure 9:  | C-5 NP Architecture                                         |

| Figure 10: | The Viper Nexperia Architecture                             |

| Figure 11: | The OMAP Architecture                                       |

| Figure 12: | The ARM MPCore Architecture                                 |

| Figure 13: | The Cell Architecture                                       |

| Figure 14: | The HW/SW Co-design Flow                                    |

| Figure 15: | Application Modeling Aspects of the Co-design Flow          |

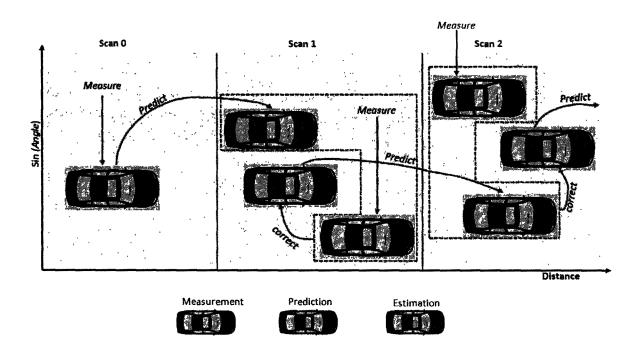

| Figure 16: | State prediction and estimation in STT                      |

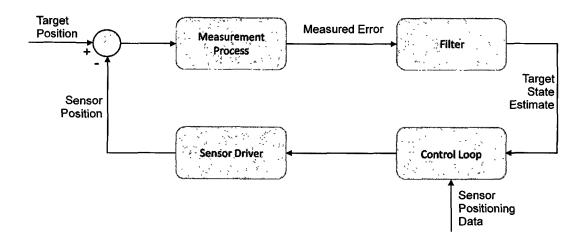

| Figure 17: | The Single Target Tracking Loop                             |

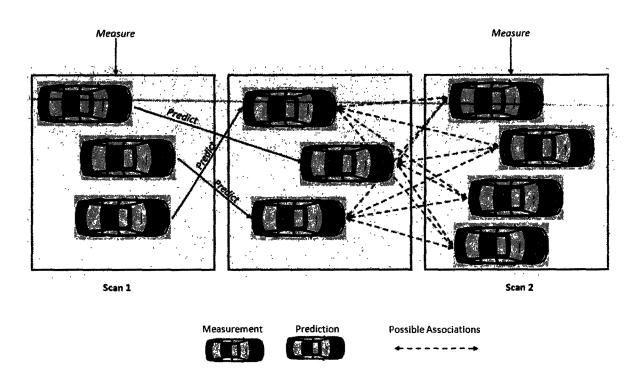

| Figure 18: | State prediction and estimation in MTT                      |

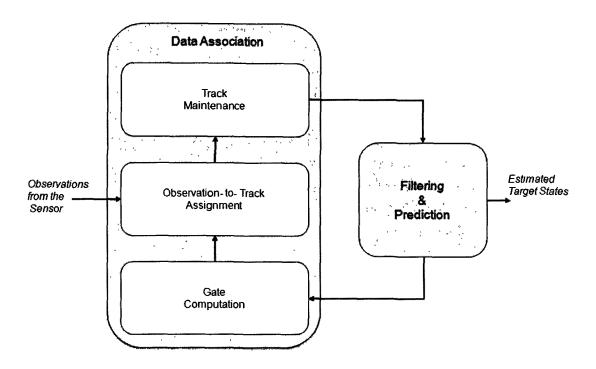

| Figure 19: | Building Blocks of a Generalized MTT System43               |

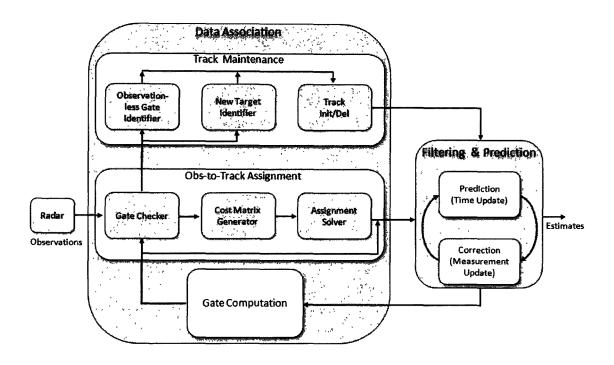

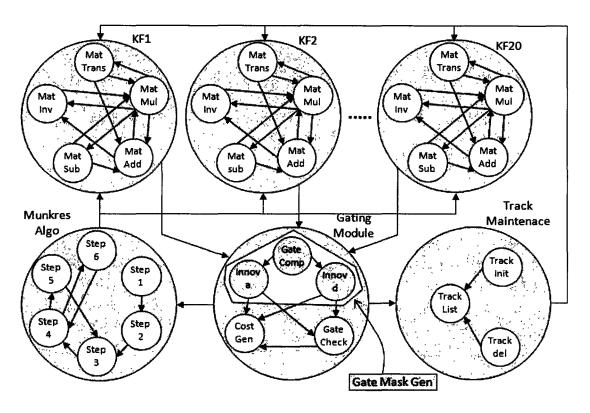

| Figure 20: | Our Design of the MTT Application                           |

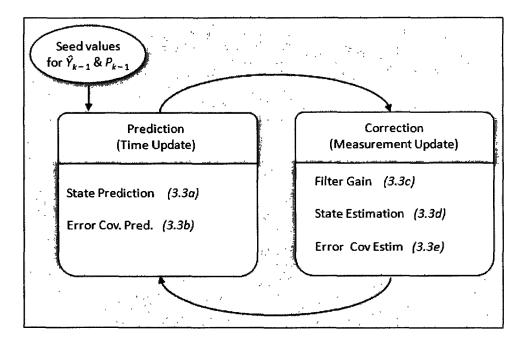

| Figure 21: | The Kalman Filter50                                       |

|------------|-----------------------------------------------------------|

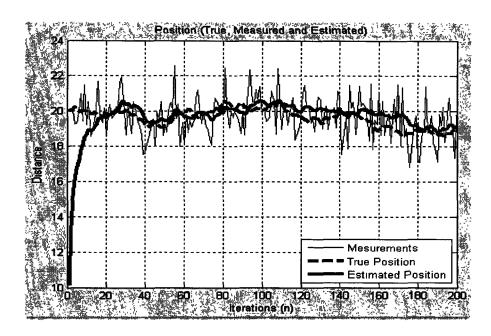

| Figure 22: | Kalman Filter Output                                      |

| Figure 23: | The Gate Checking Process                                 |

| Figure 24: | The Cost Matrix Generation Process                        |

| Figure 25: | A conflict Situation in Data Association                  |

| Figure 26: | The Munkres Algorithm for the Assignment Problem61        |

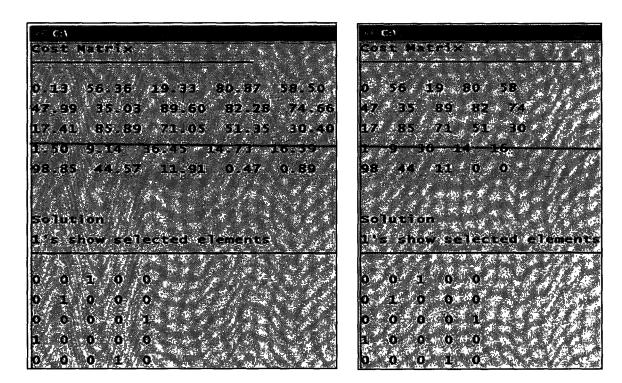

| Figure 27: | An example of the Assignment Solver Output                |

| Figure 28: | Observation 2 does not fall into any gate                 |

| Figure 29: | Gate 3 goes without any observation falling in it         |

| Figure 30: | The Architectural Aspects of the Co-design Flow72         |

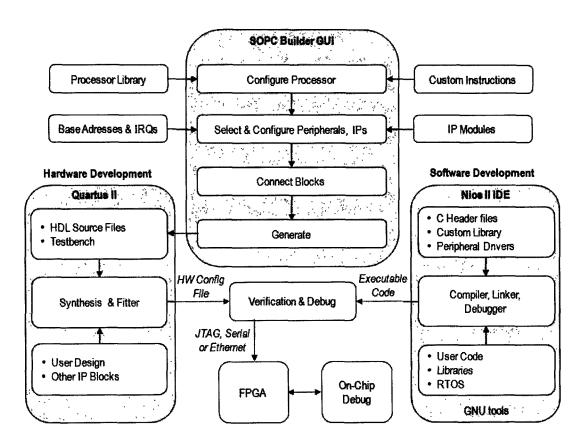

| Figure 31: | Altera's Embedded Design Suite (EDS)75                    |

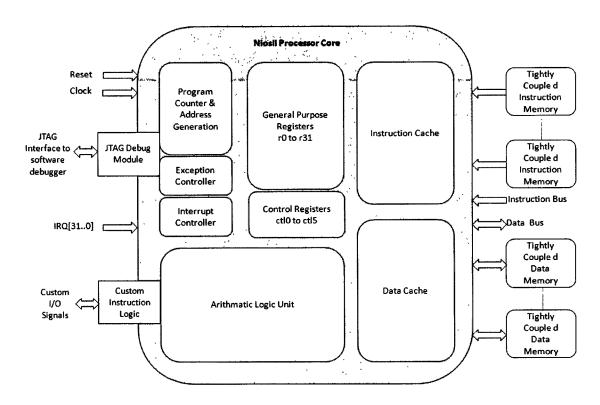

| Figure 32: | The Nios II Arcitecture                                   |

| Figure 33: | Application task structure                                |

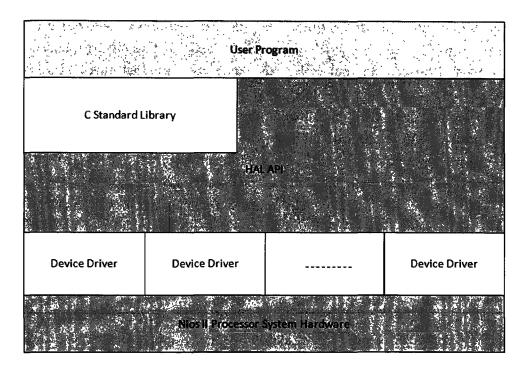

| Figure 34: | The Hardware Abstraction Layer (HAL) Structure            |

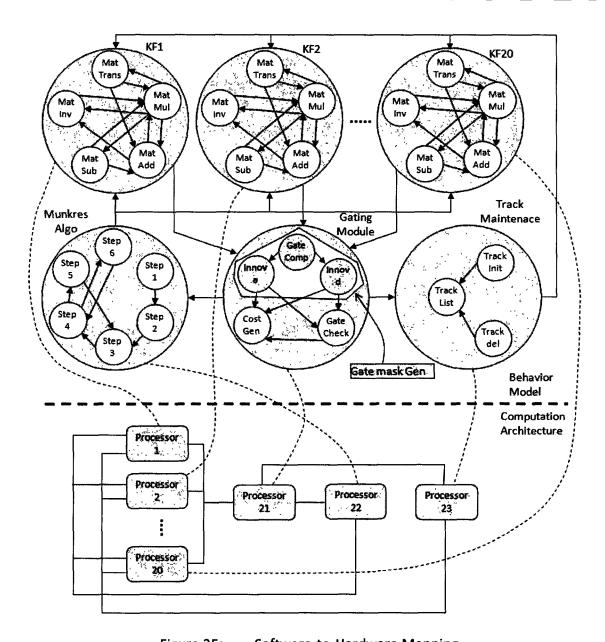

| Figure 35: | Software-to-Hardware Mapping                              |

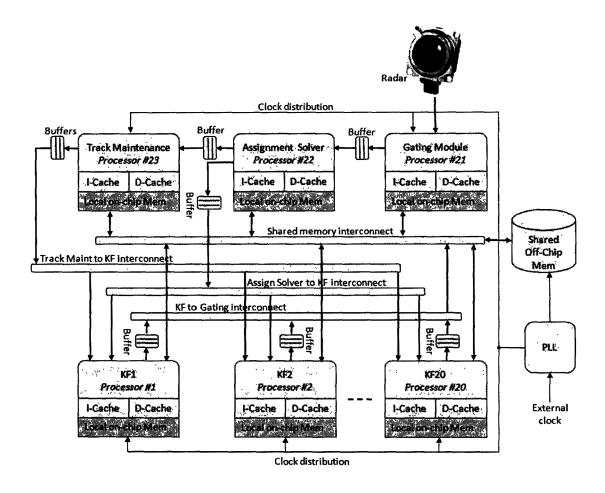

| Figure 36: | The Non-Optimized Initial Architecture                    |

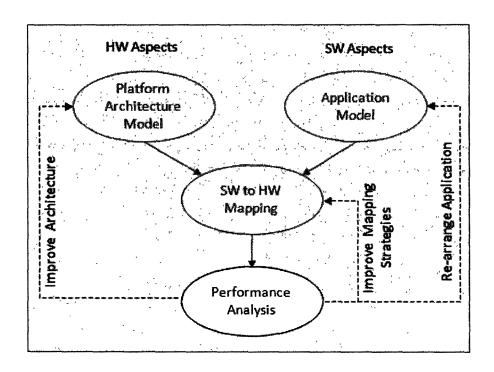

| Figure 37: | Performance Analysis and Optimization                     |

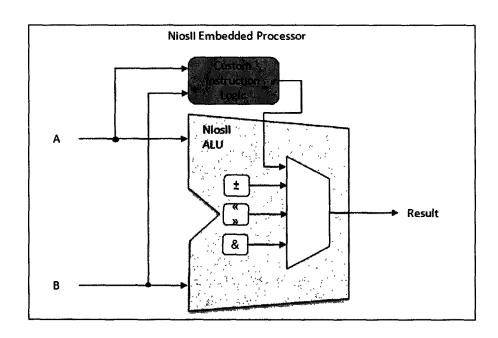

| Figure 38: | Nios II custom Instruction                                |

| Figure 39: | Cache behavior for Kalman Filter                          |

| Figure 40: | Kalman Filter Runtime Vs Cache Sizes                      |

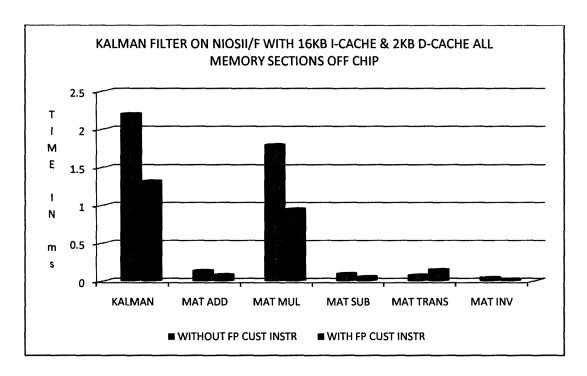

| Figure 41: | Kalman Filter performance with 16KB I-cache & 2KB D-cache |

| Figure 42: | Kalman Filter performance with FP Custom Instructions     |

| Figure 43: | Effects of on chip and off chip memory sections on Kalman Filter 10    | 80 |

|------------|------------------------------------------------------------------------|----|

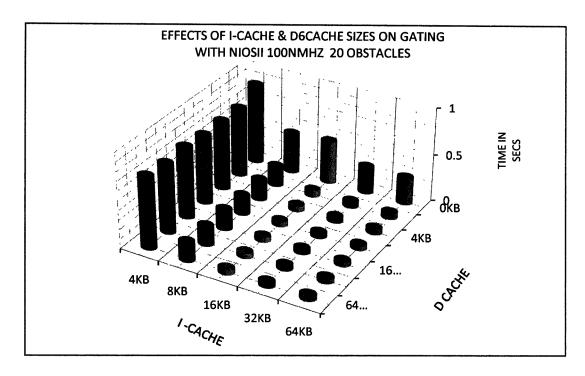

| Figure 44: | Cache behavior for Gating Module                                       | 09 |

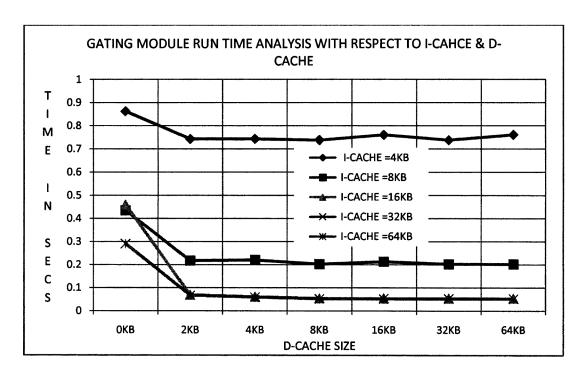

| Figure 45: | Gating Module Runtime Vs Cache Sizes                                   | 09 |

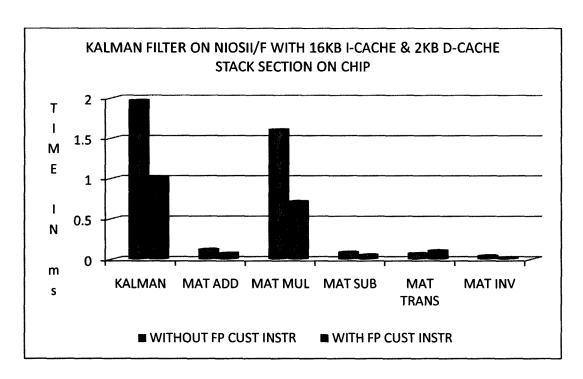

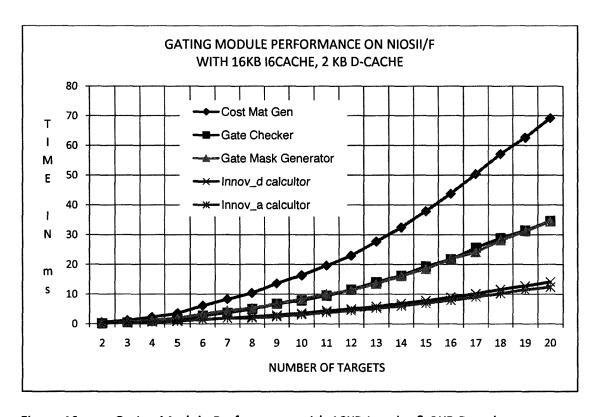

| Figure 46: | Gating Module Performance with 16KB I-cache & 2KB D-cache              | 10 |

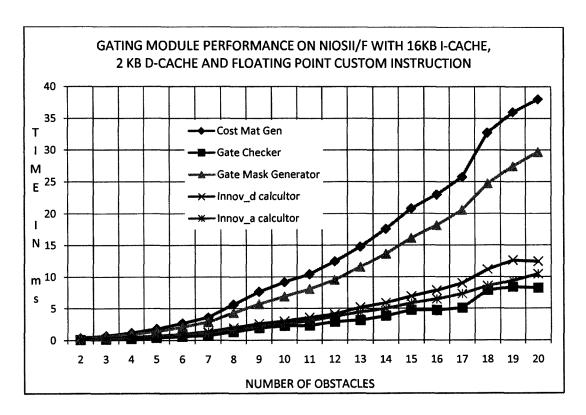

| Figure 47: | Gating Module performance with Floating Point Custom Instructions 1    | 11 |

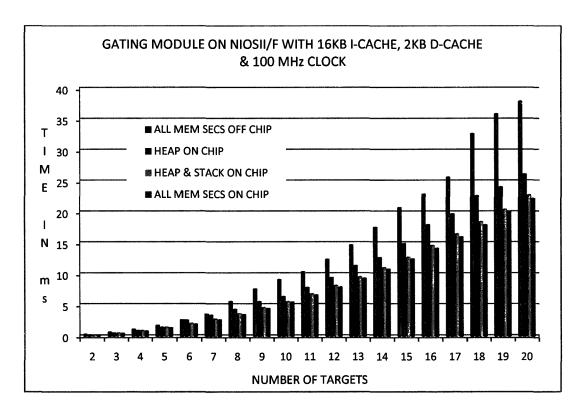

| Figure 48: | Effects of on chip and off chip memory sections on Gating Module 1     | 12 |

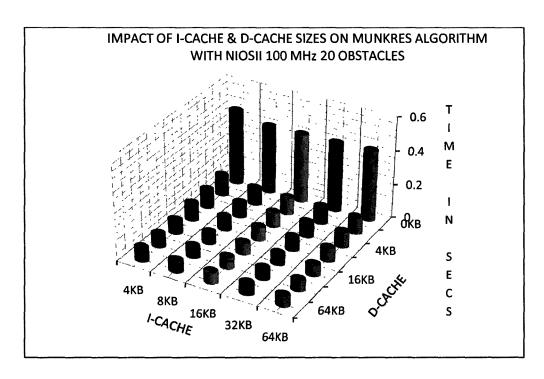

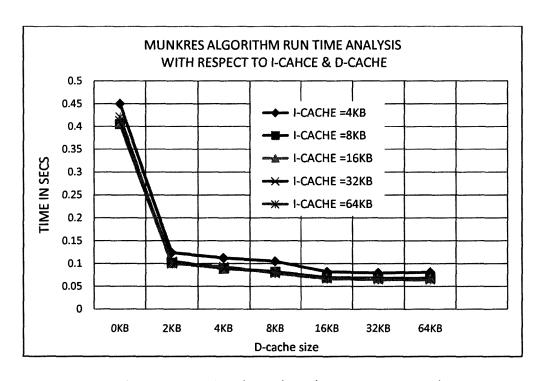

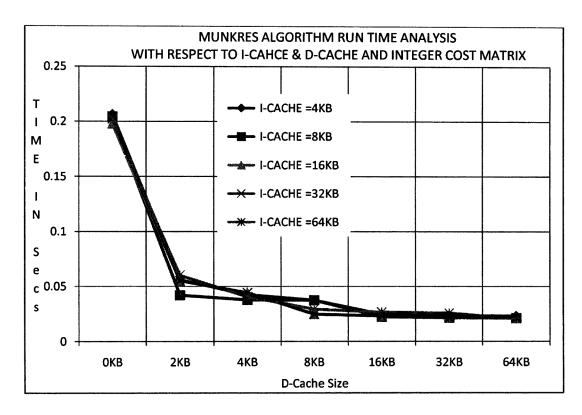

| Figure 49: | Munkres Algorithm I-cache and D-Cache Analysis 1                       | 14 |

| Figure 50: | Mankres Algorithm Runtime Vs Cache Sizes                               | 14 |

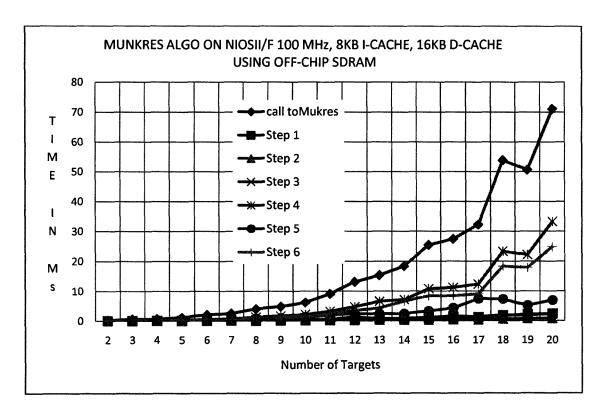

| Figure 51: | Munkres Algorithm performance with 8KB I-cache and 16KB D-Cache 1      | 15 |

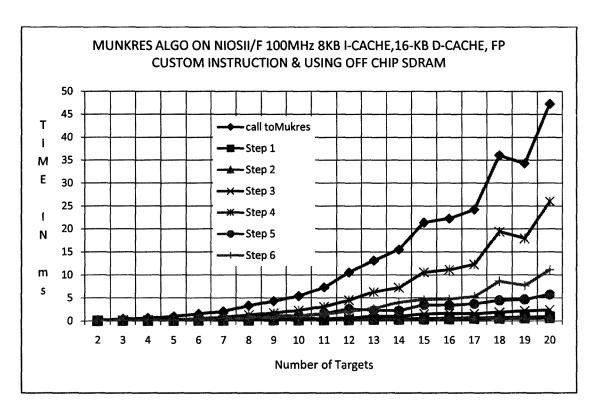

| Figure 52: | Munkres Algorith performance with Floating Point Custom Instructions 1 | 16 |

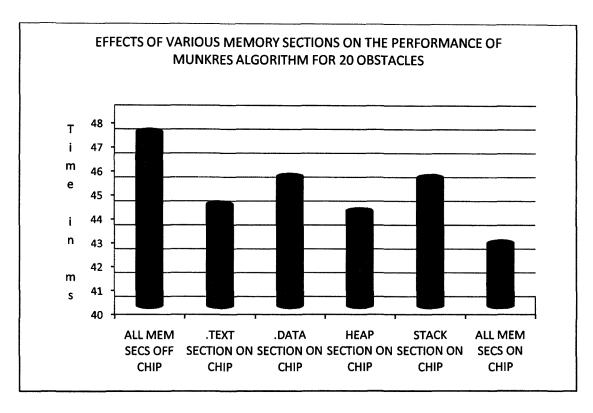

| Figure 53: | Effect of on-chip and off-chip memory sections on Munkres Algorithm 1  | 17 |

| Figure 54: | Floating point Cost Matrix versus Integer Cost Matrix 1                | 18 |

| Figure 55: | Cache Behavior for Munkres Algorithm with Integer Cost Matrix 1        | 19 |

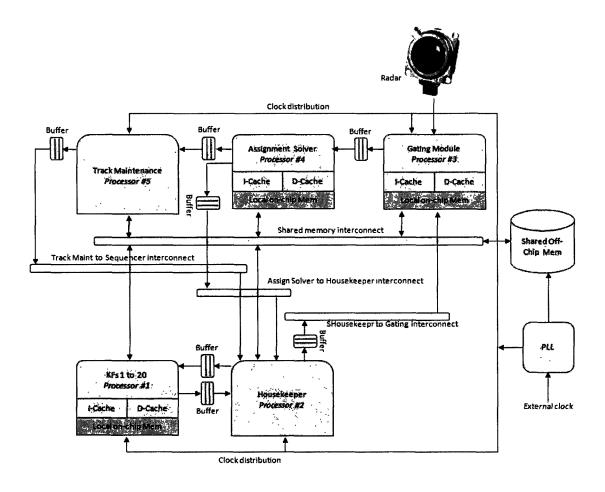

| Figure 56: | Finalized System Architecture                                          | 22 |

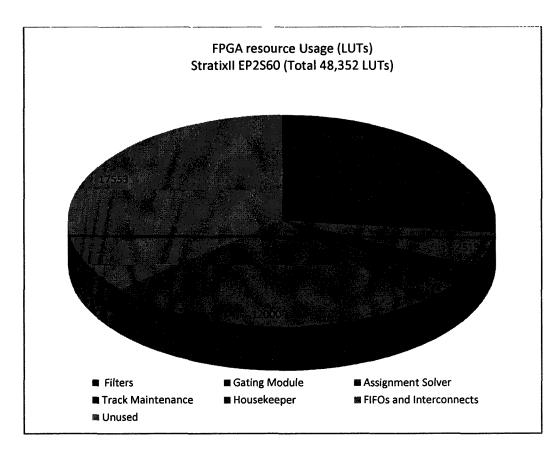

| Figure 57: | FPGA Resource Usage                                                    | 24 |

| Figure 58: | Lucent Datona Architecture                                             | 34 |

| Figure 59: | ST Microelectronics NOMADIK                                            | 35 |

| Figure 60: | 1AX Architecture with AMBA Bus                                         | 36 |

| Figure 61: | Diopsis RDT Architecture                                               | 37 |

| Figure 62: | The Nios II Softcore Processor                                         | 39 |

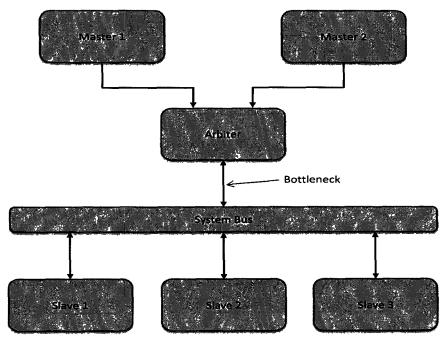

| Figure 63: | Common Bus Multi-Master Connection with Host Side Arbitration 1        | 45 |

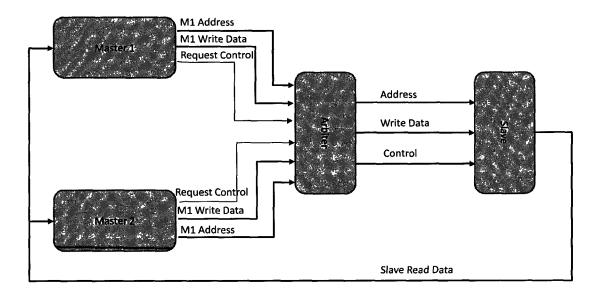

| Figure 64: | System Interconnect Multi-Master Connection with Slave Side Arbitrati |    |

|------------|-----------------------------------------------------------------------|----|

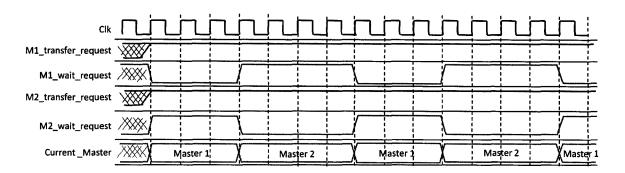

| Figure 65: | Arbitration of Continuous Transfer Requests from Two Masters          |    |

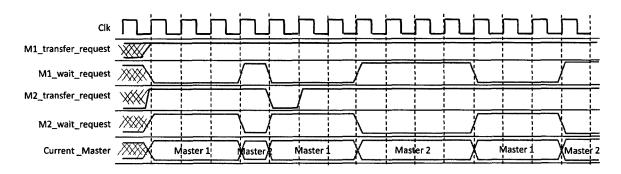

| Figure 66: | Arbitration of Two Masters with a Gap in Transfer Requests            | 47 |

1

## Introduction

Loss of any human life is tragic in any circumstances but the accidental death of a human being in his or her prime age has the most devastating effects on the emotional and social well being of the society. Unfortunately, road accidents are the number one cause of accidental deaths and the majority of their victims are in their prime age. The work presented in this document is a step towards the cause of reducing the number of road accidents and hence minimizing the loss of invaluable human lives. This introductory chapter first highlights the magnitude of this cause and then it outlines the solution we propose to serve the cause.

### 1. General Introduction

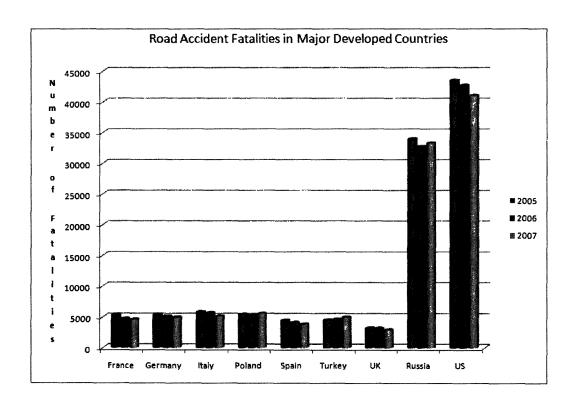

Thousands of people around the world lose their lives to road accidents every year. Thousands others get seriously injured and most of them become disabled for life. A survey showed that 94,000 people died in road accidents in 2006 in USA, Europe and Japan (1). Data (2) for the three years from 2005 to 2007 as illustrated in Figure 1, show that the road accident fatality rates in the major developed countries remain almost constant. It is not hard to imagine that the statistics are even worse in the most populous regions of the world where transportation safety structures are less developed. For example, India has the worst road fatality rate in the world. In 2004 India registered 85000 fatalities in road accidents. In the same year 130,000 people got crippled for life in India due to road accidents (3). The social, economical and psychological repercussions of these accidents are of enormous proportions. The saddest aspect of these fatalities is that most of the victims are less than 40 year old (4). Individuals in this age

group are the most productive members of society who provide, on the average, for five others dependent on them. Hence the loss of one individual in this age group not only causes emotional distress but also economical misery and suffering for those dependent on him or her. As a consequence, the damages ripple through the fabric of the whole socio-economic setup. According to a study, in the US only, the estimated cost of road accidents exceeds US \$167 billion every year (5).

Analyses have shown that most of the accidents are caused by the driver's inattention due to physical and mental fatigues. In Europe two thirds of the road accidents happen due to lack of attention on the part of the driver (1). The situation becomes even worse in low visibility conditions due to poor weather or night time driving. Correlations between collisions and driver reactions have shown that a considerable number of accidents can be avoided by recognizing a hazard in sufficient time and making appropriate driving maneuvers (6). It has been shown that if drivers reacted half a second earlier than they normally do, they would avoid approximately half of all accidents (1). The authors in (7) estimated that the crash rate could be reduced by at least 50% with some kind of warning system onboard a vehicle. An analysis (8) showed that between 37% and 74% of the collisions can be avoided by using an obstacle detection system.

Figure 1: Road Accident Fatalities in Developed Countries --- Source: (2)

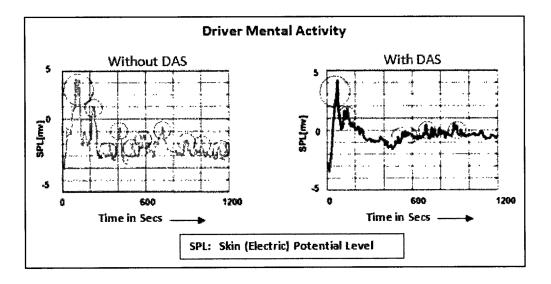

Such results can be achieved by warning signals to the driver or by automatic control of the vehicle. Electronic systems capable of alerting the driver to impending dangers in a timely manner are called Driver Assist Systems (DASs). These systems alleviate the mental pressures and physical fatigues a driver has to endure in today's driving environment. Reduced mental and physical labor guarantees a more attentive and vigilant driver. Scientific studies confirm that DASs reduce the number mental tension peaks when the driver uses an electronic warning or assistance system. Figure 2 shows the results of a study (9) done by Honda Motor Corporation for the Lane Keep Assist System. When the driver uses the DAS, he or she goes through a reduced number of mental pressure peaks and hence feels more attentive and alert to hazardous situations.

The undisputable advantages of the DASs have convinced the researchers as well as the vehicle manufactures to continue to develop more and more sophisticated systems. Governments around the world are increasingly joining hands with researchers and vehicle manufacturers to find out a way of reducing accidents and to mitigate the effects in cases where accidents cannot be avoided.

Figure 2: DAS's help reduce Drivers' Mental Stress --- source (9)

## 2. Problem Diagnosis and Our Proposed Solution

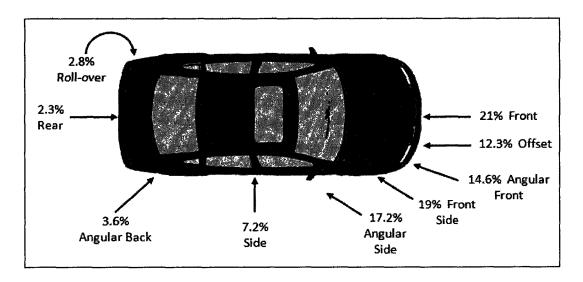

To suggest an effective solution to a problem, it is of vital to analyze the problem and diagnose its causes. Results of automotive accident profiling reported in (10) and illustrated in

Figure 3, show that frontal collisions account for 66.9 % of all automotive accidents. Hence it can be inferred that avoiding frontal collisions would result in 66.9% reduction in automotive accidents.

Figure 3: Accident Profile of an Automotive---source: (10)

It is proven that the stopping distance when braking suddenly, is 22 meters at a speed of 40 kilometers per hour and 44m at a speed of 60 km/h (11). This *Skid-to-Stop* distance increases nonlinearly with the vehicle speed in fair weather conditions. In poor weather the roads become slippery and the stopping distance increases even further. This means that regardless of the level of brake performance, the sensing of danger before the driver can respond is integral to the prevention of accidents.

A radar can sense an obstacle from a considerable distance and it works in poor weather as well as in fair weather. If the obstacle in question is not a stationary one, it is of consequential importance not only to detect it but to know its dynamic behavior and the evolution of its trajectory. Furthermore, to avoid a collision on real roads, multiple obstacles have to be monitored simultaneously. Monitoring the dynamic behavior and trajectory evolution of several objects is termed as *Multiple Target Tracking*.

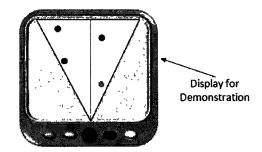

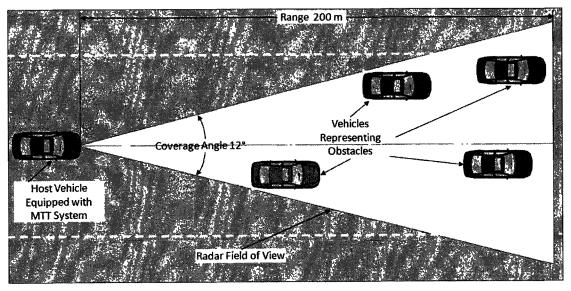

We propose a DAS based on a Multiple Target Tracking (MTT) algorithm that uses an automotive radar sensor as shown in Figure 4. We use a low-cost radar for obstacle detection and plug it into our MTT system to turn it into a precise and high performance tracker. The system can monitor upto 20 moving or stationary obstacles and generates alert signals for the ones that are dangerous. The radar is mounted on the front side of the host vehicle to detect obstacles 200 meters ahead and within the 12° coverage angle. The MTT system behind the radar tracks these

obstacles in realtime. Thus we target the 66.9% frontal collision zone and generate warning signals for the driver 200 meters before the vehicle arrives at the obstacle. So the driver has more than the half second time cited above (1), to react and take a preventive action.

To be able to rapidly process multiple targets, we use a multiprocessor architecture for the for our MTT system. To make it cost effective, reprogrammable and flexible we implement the system in FPGA using soft-core processors.

Figure 4: A simplified illustration of our proposed DAS

## 3. Plan of the Document

After introducing the theme of the subject of the thesis in this chapter, we move on to the internal details of the system in the coming chapters. In Chapter 2 we present available literature

related to our work. We give a critique of the existing solutions and compare and contrast our solution to them. In Chapter 3 we provide details of our MTT application. We explain the application's mathematical model and illustrate the key concepts used in the modeling process. In Chapter 4 we describe the software development model of the application and its mapping to a preliminary hardware architecture. We also introduce the implementation platform and the associated design and development tools in Chapter 4. In Chapter 5 we analyze the performance of the system and lay out a plan for optimizing it. Following the optimization plan, we customize the system architecture to meet the application performance requirements in the best possible way. We end chapter 5 by presenting the finalized optimum system architecture. In Chapter 6 we present the conclusions of the work and provide directions for future work.

2

## **Related Work and Motivation**

In the last several years various kinds of driver assistance systems have emerged. Some solution providers also offer electronic platforms dedicated for developing driver assistance systems. Most of these systems and platforms have limited functionalities and in most cases they are too costly to be deployed on a large scale. If the cost of these systems could somehow be brought down they may be used in conjunction with the solution we propose. Here we present some of these systems and discuss their merits and demerits.

#### 1. Introduction

This chapter describes a review of the existing academic and industrial efforts being done in the fields related to the subject of this thesis. The related work is divided into three categories according to the main themes of the thesis.

In the first category, section 2, we survey some of the general Driver Assistance Systems (DAS) available either commercially or researched academically. In this category we highlight the salient functional characteristics of these systems. We do not emphasize on underlying hardware or software architecture or the implementation details. In this section we also present a short critique of the existing solutions. At the end of the section we discuss our solution based on MTT. After introducing our MTT based solution, we discuss works related to MTT in section 3.

In the second category, section 4, we describe design platforms specifically targeting driver assistance or automotive safety applications. Here we look not only into the functional characteristics but also into the architectural and technological aspects of these systems. We

highlight the pros and cons of these platforms followed by a short description of our proposed architecture.

In the third category, section 5, we describe MPSoC architectures designed for applications other than DASs. The interest here is not the application but the design and implementation of the architectures. Here we discuss the reasons for the popularity of the MPSoCs and we argue why we do not choose fixed MPSoC architectures. At the end of the section we highlight the reasons why we prefer an FPGA platform and soft-core processors for the implementation of MPSoC.

In section 6 we present the hardware / software co-design methodology that we follow for designing our system. We conclude the chapter with a summary in section 7.

## 2. Driver Assistance Systems

Driver Assistance Systems can be classified into several categories. These categories include the Adaptive Cruise Control (ACC) systems, the Lane Keep Assistance Systems (LKAS), Lane Departure Warning Systems (LDWS), Parking Assistance systems etc. In the following sections we describe the salient features of some of the projects and systems targeting these applications.

#### 2.1. The INTERSAFE Project

The European Project PREVENT (12) was aimed at developing preventive and corrective safety systems for automotives. The effort was to prevent accidents from happening and to minimize the gravity of the consequences when the accident cannot be prevented. It is a grand collaborative project undertaken jointly various European academic and industrial partners. There are several subprojects within the main project. INTERSAFE (13) was established to support the vision of IP PReVENT to create electronic safety zones around vehicles by developing and demonstrating a set of complementary safety functions. It is based on laser scanners, video cameras and bidirectional vehicle-to-infrastructure (V2I) communication. The Laser scanner system obtains a relative position within the intersection by detecting landmarks such as posts and other similar fixed objects next to the intersection, which are registered in a digital map. The video system uses lane markings at the intersection for relative localization which are registered in a digital map. Laser scanners were integrated into both left and right front

corners of the demonstrator vehicle. Thus a combined scan area of 220 degree around the vehicle is achieved.

#### 2.2. Honda HiDS

Honda intelligent Driver Support (HiDS) system comprises of Adaptive Course Control system and Lane Keep Assist System (9). ACC is responsible for controlling vehicle speed and headway distance to a preceding vehicle. The ACC takes into account a Forward Speed of 45-100km/h. The Lane Keep Assist System (LKAS) Assistance provides steering movement to keep the vehicle in the center of its lane. The types of sensors used and the implementation details are not known.

#### 2.3. SEAT ADAS

SEAT exhibited a prototype of their system called Alhambra ADAS (Advanced Driver Assistance Systems) at the 10th World Conference on Intelligent Transport Systems and Services held in Madrid in 2003 (14). The main features are an adaptive speed regulating ACC, excessive speed warning when approaching traffic signals and road markings recognition. The vehicle is also equipped with "intelligent" headlights, which regulate the adaptive lights beam intensity according to road conditions. The ACC system automatically adjusts the cruise speed of the vehicle. It detects other vehicles, using sensors mounted in the headlights, instead of the usual radar, and maintains a safe distance by activating controls brake and accelerator.

This prototype includes the Stop & Go function, thus complementing the ACC system at low speeds (0 to 40 km/h), and automatically stopping the vehicle. Another feature is the detection of traffic signals by radio frequency. The vehicle receives information about the speed limit, warns the driver and adjusts the car speed. A fourth system "reads" the road markings using a camera. An electronic unit calculates the distance between the car and the road signs and sound alert or vibration of the steering wheel is generated to warn the driver of a danger. This performance is achieved with the help of a prediction system using a database complementary to the navigation system, including a series of parameters such as latitude and longitude of several reference points like the sidewalk or the radius of curvature, and dynamic data of the vehicle. The resulting information help regulate the speed with respect to the vehicle trajectory.

#### 2.4. The SARI / RADARR Project

The project RADARR (Recherche des Attributs pour le Diagnostic Avancé des Ruptures de la Route) is a subproject of the SARI (Surveillance Automatisée de la Route pour l'Information des conducteurs) (15) program supported by the French government in the framework of the PREDIT initiative for land transport safety. The objective of this study is to design an information system alerting drivers of a potential loss of control of their vehicle. The risk is considered linked to a physical disruption of the route in open country. One of the aspects of the project is to identify and quantify the trajectory limits on roads for vehicles which are then graded hierarchically according to the level of their dangerousness. A laser rangefinder is used for identifying the vehicle trajectory limits. The risk is assessed and then used define a typology of messages signals intended to or get the driver's attention.

Another objective of the project is to measure the trajectory of vehicles turning around a curve in the road. The measurement system is based on three digital cameras covering the vehicle from three angles: from the front, from the back and from the top. The system is equipped with a laser rangefinder that provides information on a semi-plane of the scene. Once the effectiveness of the system put is proven, it will be evaluated for deployment.

#### 2.5. The CHAMELEON project

The CHAMELEON (16) was another multi-partite project supported by the European Union from 2000 to 2002. The main objectives of the project were the development of pre-crash sensorial system for impending crash detection. The work was geared more towards the mitigation of the severity of the accident in case of an impending crash. They focused on the improvement of the sensor technologies and on the research in object classification and sensor fusion techniques. The sensors being researched were contributed by collaborating industrial partners and included laser scanners and microwave radars.

Various crash scenarios were simulated in the lab and their effects were analyzed to determine the number and types of the sensors and their respective technical characteristics necessary for minimizing the gravity of a crash.

#### 2.6. Other less known DAS's

Research on sensor fusion is also reported in (15). Here the sensors under consideration are video cameras and laser scanners. The research focuses on single object tracking with a laser scanner and pattern matching for lane and object recognition.

A concept of intelligent navigator is proposed in (17). From both the current traffic condition obtained from visual data and the driver's goal and preference in driving, it autonomously generates advice to the driver. These advices include safety related and tactical maneuvers such as emergency braking due to an abrupt deceleration of the front vehicle, lane changing due to the congested situation etc. A Three-level reasoning architecture is proposed for generating advice in dynamic and uncertain traffic environments.

An active vision system for realtime traffic sign recognition system is presented in (18). The system is composed of two cameras; one is equipped with a wide-angle lens and the other with a telephoto lens, and a PC with an image processing board. The system first detects candidates for traffic signs in the wide-angle image using color, intensity, and shape information. For each candidate, the telephoto camera is directed to its predicted position to capture the candidate in a larger size in the image. The recognition algorithm is designed by intensively using built-in functions of an off-the-shelf image processing board to realize both easy implementation and fast recognition.

### 2.7. Critique of the Presented DASs

The DAS presented above are effective but there are some practical issues that have to be addressed. For example, the INTERSAFE (13) is limited to road crossings only. Secondly, the laser scanners and cameras rely on the land marks in a digital map. The land marks are very likely to change over time and the digital map must be updated on all the systems in the field. The use of cameras for road mark identification has its own limitations. For example they are ineffective in poor weather conditions. Similarly the range of cameras is very short implying that for identifying an object; the host vehicle must get close to the object. This can be highly dangerous when the host vehicle is running at high speed or when the road is slippery due to rain or snow. Most of all this solution relies on an infrastructure that must be placed at every road crossing. This, obviously, is a very costly proposition due to its initial fixed cost and the recurring maintenance cost.

The Honda HiDS (9) sounds interesting but since the technical details are not known, it is hard to evaluate it. Moreover systems like HiDS are not only proprietary and limited to the specific vehicle models, but they are also very costly often more than or comparable to the cost of the vehicle itself. Hence driver of a vehicle different than the specific model cannot use these systems while the costs of the specific equipped models are not in the budgetary range of everybody.

The system proposed by SEAT (14) works more or less on the same lines as the INTERSAFE (13) with the addition of the ACC. So it has all its limitations discussed except that the SEAT system can keep a safe distance from an obstacle. Furthermore being limited to specific high-end SEAT models, it has the same disadvantages as the Honad HiDS.

The SARI/RADARR (15) project seems to be concerned more with road profiling than developing an onboard safety mechanisms. It does propose the generation of a warning signal to the driver when the driver departs from the predefined safe trajectory or when the vehicle approaches a curve on a pre-charted road. What happens when the road is not already charted or when the drivers stays on the defined trajectory but there is an obstacle ahead, is not considered. In a way it is dependent on it is dependent external on actors like the INTERSAFE (13).

The CHAMELEON (16) project is concerned with damage control rather than damage prevention. It discusses the safety mechanisms and sensors which may minimize the damage when the crash is inevitable. Preventing the crash from happening is not among the objectives of the project. Solution like these can be used to complement crash prevention systems so that the damage can be reduced when it is not possible to avoid the crash.

Most of the other less know systems are almost exclusively using cameras and vision systems to alert the driver to a potentially critical situation. As discussed above, camera based systems are not effective in all conditions.

### 2.8. Our Proposal

We propose a DAS based on a Multiple Target Tracking (MTT) algorithm that uses automotive radar as a front end sensor. An MTT system monitors the dynamic behavior of several obstacles at a time. In the context of Driver Assistance Systems, an MTT system detects obstacles in front of the host vehicle and monitors their distance, speed and trajectory. If the behavior of any of the obstacle fulfills preset alert conditions, the driver of the host vehicles is alerted in advance to deal with any dangerous situation. In case the vehicle is fully equipped for autonomous driving, the signals generated by the MTT can also be used to automatically control the vehicle if necessary. The alert signals generated by the MTT system can also be used to

trigger the onboard safety systems if the obstacle's behavior is rated above a predefined danger level. So it also can incorporate the pre-crash safety mechanism when the crash cannot be avoided at all.

We use a low-cost radar for obstacle detection and plug it into our MTT system to turn it into a precise and high performance tracker. The tracking algorithm helps differentiate between real danger and false alarms, so that the driver is not panicked by triggering alert signals unnecessarily. Another advantage of the tracking algorithm is that can cancel the interference for other similar or dissimilar systems. The system we propose can monitor upto 20 moving or stationary obstacles and generates alert signals for only the ones that are really dangerous.

The use of radar as sensor in our system has the advantages of longer range as compared to camera based systems. It performs better in bad visibility conditions and has lower computational requirements (19). It is an all weather system that works as efficiently in a stormy dark night as in a sunny bright day. Moreover, since radar helps detect obstacles at longer distances, it ensures longer time for vehicle drivers to react to a dangerous situation.

Our system is applicable on highways with sparse high speed traffic as well as on the urban roads with dense low speed traffic. It does not rely on any infrastructure or digital maps.

We propose a plug and play system so that it is not limited to any specific vehicle manufacturer or a vehicle model. The low cost of the system makes it accessible to every vehicle driver.

## 3. Work Related to Multiple Target Tracking

Studies have been done on the isolated parts of MTT system (20), (21) but, to the best of our knowledge, design of the complete MTT based DAS has not been addressed in full before. Some work has been done on different isolated components of the MTT system but in different contexts. For example an implementation of the Kalman filter which is a part of MTT, is proposed in (19). It is not only limited to the filter but it also is a fully hardware implementation. Fully hardwired designs lack the flexibility and programmability needed for the ever evolving modern day embedded applications. Moreover, the authors report two alternative implementations of the Kalman filter namely the Scalar-Based Direct Algorithm Mapping (SBDAM) and the Matrix-Based Systolic Array Engineering (MBSAE). The former consumes 4564 logic cells whereas the latter consumes 8610 logic cells for a single filter each. Apart from the large sizes, the internal components of both the implementations are manually organized and

re-organized to get the desired performance. This is obviously not scalable and repeatable in a complex system like ours where the filter is not the only component to be optimized.

An attempt to implement an MTT system in hardware for a maritime application is documented in (22). In addition to being a completely hardwired implementation, the work presented here is inconclusive.

The data association aspect of MTT has been dealt with nicely in (21) but the physical implementation of the system is not a consideration in this work. Only Matlab simulations are reported for that part of the MTT.

Although the title of (23) sounds very close to our work, yet this work describes the theory of the Extended Kalman Filter (EKF) with a smoothing window. The paper discusses the velocity estimation of slow moving vehicles and emphasizes on the necessity of reducing the liberalization errors in the process. While the paper presents a viable solution to the problem of liberalization errors in EKF, the physical implementation of the EKF or the tracking system does not figure among the objectives of the work.

A systolic array based FPGA implementation of the Kalman filter only, is reported in (24). This work concentrates on the use of a matrix manipulation algorithm (Modified Faddeev) for reducing the complexity of the computation. This article again, presents an interesting account of implementing the Kalman filter in an efficient way. In cases where very fast filtering is the main objective, this may be a good solution.

In fact software forms of the algorithms like EKF (23) and Modified Faddeev based implementation of the Kalman filter (24) can be easily integrated into our system. For example EKF is useful in situations where a target exhibits a abrupt changes in its dynamic behavior as in hilly regions where roads curve and bend frequently. Similarly, other algorithms like (24) can be added on if required. So the works discussed above can be considered as complementary rather than competitors to our work.

Most of the available works treat the individual components of the MTT (mainly the Kalman filter) in isolation. However, putting these and other components together to design a coherent MTT application and adapting it to automotive safety utilization, is not a trivial task.

## 4. Platforms for Automotive Applications

Some of the vendors provide electronic development platforms for driver assistance systems. These platforms include programmable processors, heterogeneous multiprocessor

systems and microcontrollers dedicated to a certain type of driver assistance application. In the following sections we describe some of the available platforms.

#### 4.1. IMAPCAR

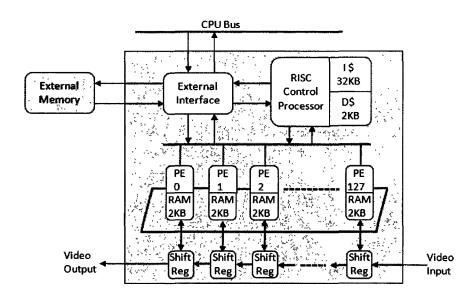

NEC upgraded the IMAP-VISION processor to IMAP-CE, which was unveiled at the ISSCC held in 2003 in the United States. The processor was renamed IMAPCAR (Integrated Memory Array Processor for CARs) (25) in 2006. It is used by Toyota Lexus in their cars (26) as a safety system.

IMAPCAR uses an SIMD system for which 128-parallel processing units follow identical commands and a 4-way VLIW system capable of simultaneous execution of four commands in one cycle. Each processing element has a RISC architecture with a 24-bit multiply and accumulate unit is equipped with 2 Kbyte SRAM for unit to enhance execution performance. The processor elements are interconnected via a shift register style ring network. A single 16-bit RISC control processor with 32KB program and 2KB data caches is used to control the 128 processing elements.

Figure 5: The IMAPCAR Architecture

In December 2008 (27) NEC announced the second generation IMAPCAR2 processors with support for both SIMD and MIMD operations. The 128 processing engines now support 16bits rather than 8-bits supported the earlier SIMD-only IMAPCAR.

The IMAPCAR processor is primarily aimed at the image processing requirements of the automotive safety systems. An image is loaded column wise into the 128 local memories. A processing element has therefore direct access to all pixels in a column of the picture. One of the shortcomings of the IMAPCAR design is that it is not easy to exploit the task level parallelism found in high level image processing tasks.

# 4.2. EyeQ2

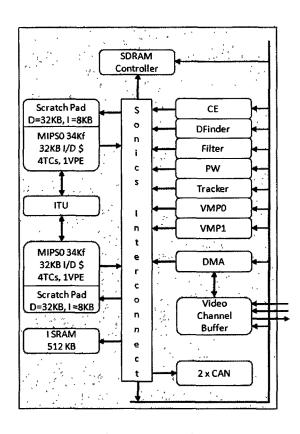

The EyeQ2 is a joint venture by Mobileye and STMicroelectronics (1). It uses two floating point MIPS32 34Kf processor cores. The two MIPS cores exchange data using the ITU (Inter Thread Communication Unit). Besides the two MIPS cores the EyeQ2 includes seven vision computing engines, and a 16-channel direct-memory-access (DMA) controller.

Figure 6: The EyeQ2 Architecture

The vision computing engines are fixed logic processing elements or hardware accelerators used for image pre-processing, object classification etc. The vision computing engines available in the EyeQ2 are CE (Classifier Engine), DFinder (Disparity Finder) which is used for stereo vision, Filter, PW (Preprocessor Window), Tracker which is used for motion analysis and two Vector Microcode Processors (VMPs) which utilize parallel vector, scalar and table lookup units.

The two MIPS cores and the seven vision computing engines are connected with an interconnection network from Sonics called SMX (Sonics Multi-service eXchange). The engines and CPU logic perform all of the vision computations required by applications such as pattern matching and image classification. The system interfaces to the outside world through two CAN controllers.

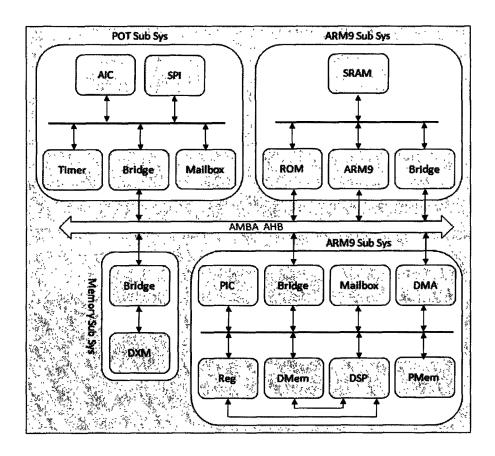

### 4.3. VIP-II

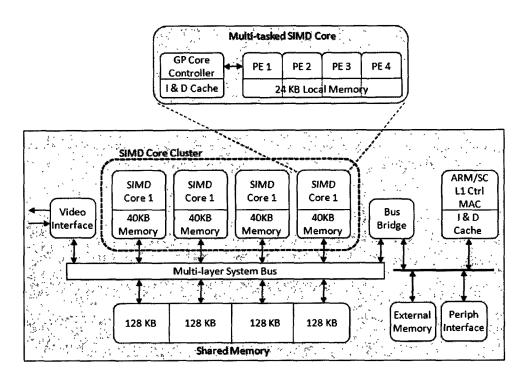

The VIP-II (Vision Instruction Processor version 2) is the successor of the VIP-I developed by Infineon (28).

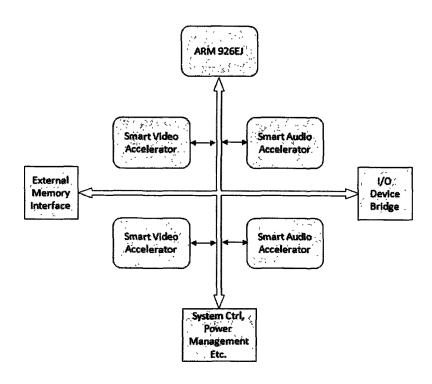

Figure 7: The VIP-II Architecture

The processor is designed for vision based automotive safety applications. The VIP-II features 4 multi-tasked SIMD cores and an ARM 9 processor. Each SIMD core consists of a general-purpose core and four PE (processing element) arrays. The cores use VLIW instructions to perform arithmetic operations and memory access in parallel. Each processing element has 4-stage pipeline. Data dependencies between the pipeline stages are avoided because each of the pipeline stages operates on an instruction from a different thread. To make this possible each processing element is provided with four instruction caches, four register files and four program counters.

Every SIMD core is controlled by a general purpose core. The four cores are connected via a multi-layer system bus. An additional general purpose processor (ARM9) handles the communication tasks and main control flow. The four general purpose controllers within the SIMD cores and the ARM9 are all programmed in C. To program the SIMD cores a C language extension, called DPCE (Data Parallel C Extension), is used.

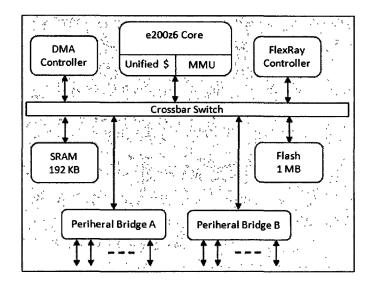

### 4.4. MPC5561 Microcontroller

Designed by Freescale Semiconductor (29), the MPC5561 MCU is a member of the MPC5500 family of microcontrollers. It features a FlexRay network controller and Freescale's e200 core, which is customized for automotive safety applications. The e200 core has a 32-bit PowerPC architecture with additional signal processing instructions. It has a 32KB unified cache, a Memory Management Unit (MMU) and a 32-channel DMA. It has interfaces for 192KB SRAM and 1MB Flash memory apart from the conventional microcontroller peripherals like timers, watchdog etc. The FlexRay is a communications system designed to provide distributed control for automotive applications. It has a dual-channel architecture for redundancy for the reliability requirements of safety systems. The FlexRay is yet another networking scheme for automotive applications. The other well known schemes are CAN (Controller Area Network) and LIN (Local Interconnect Network).

The e200 core is connected to the memories, the DMA controller and the Flexray network controller through a crossbar switch. Two bridges interface the external peripherals to the crossbar.

Figure 8: The MPC5561 Architecture

### 4.5. TMS570F

In November 2008 Texas Instruments announced the TMS570F (30) microcontroller unit (MCU). It is claimed to be industry's first dual core Cortex-R4F processor-based floating-point MCU that allows automotive system designers to implement both single and double precision floating point math depending on performance requirements. According to the report it uses accelerated multiply, divide and square root functions to improve system performance. The TMS570F MCU platform uses two identical ARM Cortex-R4F processors combined with an initial two Mbytes on-chip flash memory. Industry standard peripherals include FlexRay protocol controller, up to three CAN and two LIN modules along with TI's timer co-processor and two 12-bit analog to digital converters (ADC). Targeted applications include chassis control, braking, electronic vehicle stability and steering and airbag electronics etc. Architectural details of the MCU are not provided by TI.

# 4.6. Critique

The first three of the processors described above are solely dedicated to vision based safety and assistance systems. As mentioned earlier, vision based systems are only fair-weather

and short range systems. Their performance degrades considerably in poor weather and long ranges.

The IMAPCAR (25), (27) does not support task level parallelism exploitable in most of the DAS applications. It is provided to vehicle manufactures only hence everyone cannot benefit from it. It is programmed in a C language extension specially developed for this architecture, which is called 1DC (one dimensional C). This is another disadvantage which limits the designers to the single proprietary development environment and increases the cost of the already costly system even further. Furthermore, the architecture is not reconfigurable and hence inflexible and un-scalable.

The EyeQ2 (1) also has the same restrictions as the IMAPCAR. The architecture is mainly designed for pixel level parallel processing of the images captured by the camera. Furthermore, the platform is provided to vehicle manufacturers exclusively. This makes its application highly restricted and out of the reach of the everyday vehicle users.

The vision computing engines are fixed in hardware and carry out specific image processing tasks. To scale the system for future evolutions would necessitate complete redesign of the architecture. The processor is provided only to the vehicle manufacturers like Volvo and BMW who use them in the expensive high-end vehicles.

To program the SIMD cores in the VIP-II (28), a C language extension, called DPCE (Data Parallel C Extension) is used which makes it costly and difficult to program. Thus it can be afforded by only a minority of the drivers who can afford such costly vehicles. To help reduce the high accident rates the DAS's must be economical enough to be within the reach of all the vehicle owners.

The latter two of the processors discussed above are microcontrollers targeting automotive safety measures in pre-crash situations. Such systems can complement driver assistance systems rather than replace them. The MPC5561microcontroller (29) is meant for controlling various automotive safety mechanisms and interconnecting intelligent devices onboard a vehicle. It is not a driver assistance system per say, rather it can be considered as a pre-crash damage mitigation system. The TMS570F (30) also falls in the same category as the MPC5561. It also concentrates on protective measures in case of an accident. Therefore these systems can be used in conjunction with sophisticated DAS's for assuring security of the passengers in cases where accidents cannot be avoided.

# 4.7. Our Proposal

Our work is unique in several aspects. We propose radar based DAS implemented as an MPSoC. We customize each of the processors according the needs of the application task it is

running. It makes the system fast, small sized and energy efficient. The individual processor can be separately programmed allowing for in system upgrading and improvement. The system designer can replace one algorithm with another for a specific task to make the system perform more efficiently and/or more accurately. The programming is done plain ASCII C, so tweaking the existing application or adding more functionality does not require a specialist in platform specific languages. Thus it can evolve very easily with advances in technology and with improvements in application algorithms. Moreover, the use of several concurrently running processors meets the overall real time deadlines. Several low frequency processors running concurrently consume less power compared to a single processor with a high clock frequency and doing the same job (26). Our reconfigurable MPSoC architecture of the system is inherently flexible, programmable and scalable. Adding additional processing elements or auxiliary hardware components does not affect the working of the existing architecture. reconfigurability of the processors and other components in our design, allow for customizing them according to application requirements while keeping the hardware size as small as possible. The system we propose is a complete plug-and-play solution that can be easily integrated with the existing electronic systems onboard any vehicle.

# 5. MPSoC Architectures for Other Applications

Several multiprocessor systems have been designed to target applications other than the driver assistance systems. Although the applications, for which these systems are intended, are different than our application, their architectures are of interest to us. The systems presented in the following sections have multiprocessor architectures, an attribute they share with our work.

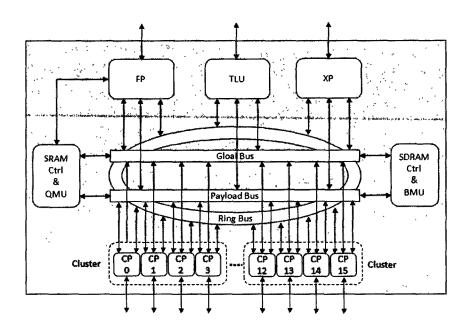

### 5.1. C-5 NP

The C-5 NP is specifically designed by Freescale Semiconductor Incorporation (31), for communications applications. It deals with the networking tasks like packet processing, table lookup processing, and queue management. The C-5 NP contains 18 processors (16CPs, XP, and FP) and three coprocessors that operate as shared resources for the CPs and each other, and perform networking-specific tasks. The programmable Channel Processors (CPs) are responsible for receiving, processing, and transmitting cells or packets. The Executive Processor (XP) provides network control and management functions in user applications. The Fabric Processor

(FP) manages the high-speed fabric interface. The Buffer Management Unit (BMU) manages centralized payload storage during the forwarding process. The Table Lookup Unit (TLU) provides table search and associated data storage services to the CPs, XP, and FP. The Queue Management Unit (QMU) manages application-defined descriptor queues among the CPs, FP, and the XP.

Figure 9: C-5 NP Architecture

The C-5 NP also contains three independent data buses that provide internal communication paths between the eighteen processors (16CPs, XP, and FP) and the three coprocessors, supporting concurrent processing. The Payload Bus is a slotted, multichannel shared, arbitrated bus which carries payload data and payload descriptors between the processors and the BMU and QMU. The Ring Bus provides bounded latency transactions between the processors and the TLU. It also supports inter-processor communication. The Global Bus is also a slotted, multichannel, shared, arbitrated bus Supports inter-processor communication via a conventional flat memory-mapped addressing scheme.

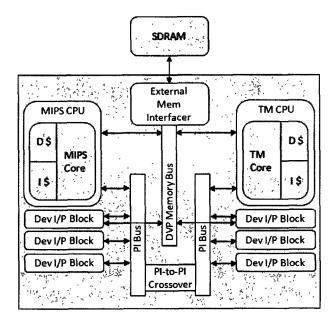

### 5.2. Viper Nexperia

The Phililps Viper Nexperia (32) is an MPSoC designed for multimedia applications. Its architecture includes two CPUs: a MIPS (R3940) and a Trimedia (TM32) VLIW processor. The MIPS acts as a master running the operating system, whereas the Trimedia runs video processing functions and acts as a slave that carries out commands from the MIPS. The system includes three buses, one for each CPU and one for the external memory interface. A 64-bit memory bus is used by the MIPS and TM32 CPUs and on-chip blocks requiring memory access. Two PI buses and a crossover PI-to-PI or memory-mapped I/O (MMIO) bridge enable each processor to control or observe peripheral block status. Hardware accelerators for image composition, scaling, MPEG-2 decoding and video input processing are also attached to the buses. The Viper can implement a number of different mappings of physical memory to address spaces. Programmable CPU cores allow new features, services, or standards to be supported through software upgrades without changing silicon.

Figure 10: The Viper Nexperia Architecture

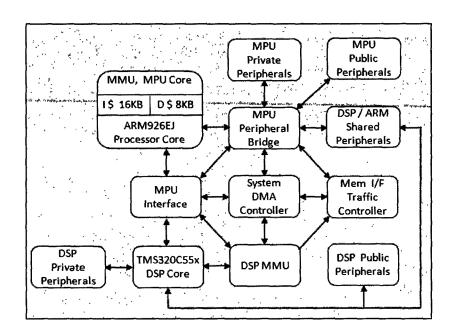

### **5.3. OMAP**

The Texas Instruments OMAP (Open Multimedia Applications Platform) (33) is designed for mobile phone wireless and multimedia applications. OMAP comes in many flavors.

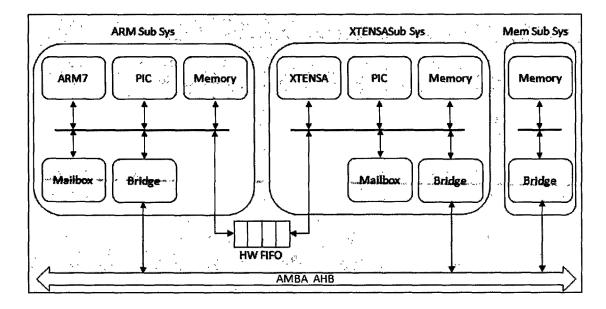

The OMAP5912 architecture contains a TMS320C55x DSP core from TI and an ARM925T CPU. The ARM acts as a master, and the DSP acts as a slave. The ARM is used for the operating system, user interface, and OS applications. The DSP is used for signal processing applications, such as MPEG4 video, speech recognition, and audio playback. Both processors utilize an instruction cache and a memory management unit (MMU) each, for virtual-to-physical memory translation and task-to-task memory protection.

Figure 11: The OMAP Architecture

#### 5.4. ARM MPCore

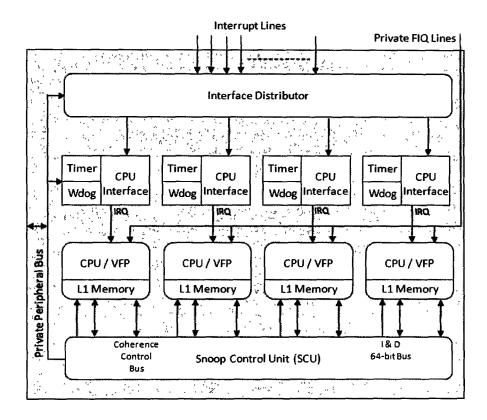

The ARM MPCore (34) is a homogeneous multiprocessor that also allows some heterogeneous configurations. The architecture can accommodate up to four CPUs. Both the data and instruction caches can be sized between 16KB and 64KB for each processor. The caches snoop for consistency. The interconnection fabric can be configured either as dual or single 64-bit AMBA 3 AXI bus. Each processor can also be configured with an optional Vector Floating Point (VFP) unit.

Some degree of irregularity is afforded by the memory controller, which can be configured to offer varying degrees of access to different parts of memory for different CPUs. For example, one CPU may be able only to read one part of the memory space, whereas another part of the memory space may not be accessible to some CPUs.

Figure 12: The ARM MPCore Architecture

### 5.5. The Cell processor

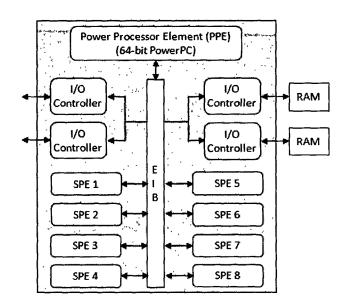

The Cell architecture (35) is designed by Sony, Toshiba and IBM for the PlayStation 3. It is comprised of hardware and software "cells". The software cells consist of data and programs (known as jobs or apulets), these are sent out to the hardware cells where they are executed.

The architeture contains a main core called Power Processing Element (PPE) and 8 special cores called Synergistic Processing Elements (SPE). The PPE is a classic 64 bit PowerPC processor with 512K cache. The processing elements, PowerPC, and the I/O interfaces are connected by the Element Interconnect Bus (EIB), which is built from four 16-B-wide rings. Two rings run clockwise, and the other two run counterclockwise. Each ring can handle up to three non-overlapping data transfers at a time.

The PPE runs the operating system and most of the applications but compute intensive parts of the OS and applications are offloaded to the SPEs. An SPE is a self contained vector processor which acts as an independent processor. Every SPE contains 128 x 128 bit registers, four (single precision) floating point units and four Integer units. The SPEs also include a small 256 Kilobyte local store (LS) instead of a cache. The SPEs have very fast access to their LS but to access the main memory they must request the interconnection bus for asynchronous transfers. Each core can be explicitly programmed with independent threads. The memory is shared and the user has to manage data copying among the cores. Like the PPE the SPEs are inorder processors and have no Out-Of-Order capabilities.

Figure 13: The Cell Architecture

### **5.6.** Discussion and critique

The systems discussed above and many other emerging application specific systems demonstrate the popularity of the multiprocessor architectures tailor made for the applications they are running. This ever growing popularity of the MPSoCs is caused by some serious limitations uniprocessor systems have.

Uniprocessor architectures have hit the wall with respect to performance and power consumption in the past decade. They, even with the highest clock speed, cannot keep up with the real-time processing requirements of the modern day embedded applications. Real-time systems require "real" parallelism and concurrency in the execution of applications (36).

Uniprocessor architectures provide "apparent" concurrency through the use of Multi-tasking operating systems but the applications are still running sequentially on the underlying hardware. Consequently they are too slow for today's complex real-time embedded applications. In reaction to these issues, Multiprocessor System-on-Chip (MPSoCs) architectures have emerged as an alternative means for achieving higher performance.

An MPSoC uses multiple processing cores operating in parallel performing various tasks to execute a complex global application efficiently and rapidly. MPSoCs provide real concurrency by segregating tasks and running them in parallel to improve predictability and performance. Energy consumption can be efficiently managed in MPSoCs by allowing processors to idle when their tasks are finished.

Heterogeneity is one of the greatest advantages of these systems because it improves realtime performance and predictability. For example, some operations in an application are standardized and can be implemented in conventional ways. However there are many specialized operations which need specialized units for higher throughput. Specialized units are tailor made according to the performance of the specific operations and hence are power efficient and their behavior is more predictable compared to a general purpose processor.

Memory subsystems for MPSoCs are custom built for the requirements of the tasks the processors are executing. They combine off-chip bulk memory with on-chip specialized memory. This not only improves performance but the memory traffic can also be easily regulated to further reduce energy consumption.

A multi-core device, which combines two or more processors on a single die, offers increased performance over single-core devices. In comparison to a traditional processor, dual-core system offers at least double the performance at the same clock frequency. Tests on a dual-core system reported in (28), have shown that the same performance can be achieved at 200 MHz as a single-core system operating at 500 MHz.

An important side benefit of the improved performance is that the power consumption and heat generation of a multi-core device are lower for the same level of performance as a single-core device. In addition, the faster clock of the single-core device requires faster memory, which further increases the power consumption and requires special packaging to dissipate the heat.

### 5.7. Our proposal

While the advantages of the multiprocessor architectures are undisputable, there are some very fundamental decisions that must be taken before initiating an application specific

multiprocessor project. The implementation platform, the types of processors, the memory hierarchy, the interconnection framework and other components have to be determined very carefully according the needs of the application.

We use FPGAs as the implementation platform for our MPSoC. FPGAs provide enormous raw processing power compared with standard microprocessors. They give the designer the choice to run applications in hardware and in software when configured with a processor IP core. Thus FPGAs provide the flexibility of reconfiguration and the liberty of reprogramming. These are two highly sought after features needed for system evolution that neither general purpose microprocessors nor ASICs can provide. General purpose microprocessors can be reprogrammed for a desired application but their hardware architecture cannot be modified. Moreover they are slow because of the sequential execution of the code. On the other hand ASICs are fast but their architecture is cast in concrete for one specific application hence they are absolutely inflexible. FPGAs combine the best of the two worlds. They can be configured with soft-core processors which can execute a software application and thus offer the versatility of a general purpose processor. They can also be configured with hardwired circuitry and thus provide high speed execution where needed. FPGAs can even have a mix of programmable soft-core processors and hardwired circuitry to accelerate certain parts of the application for achieving higher processing speed.

System performance can be easily scaled at any phase of the design cycle by adding processors, custom instructions, hardware accelerators, and by leveraging the inherent parallelism of FPGAs (37). FPGAs are highly receptive to IP reuse and support designing and verifying new customized IPs. FPGA designs using pre-verified IPs reduce system design and verification time. FPGA designs do not have the up-front Nonrecurring Engineering (NRE) costs which is characteristic of ASIC designs.

The choice of the FPGA platform allows us to use soft-core processors and IPs in our design. An FPGA designer can configure a group of programmable logic blocks to act as a processor. These are typically called "soft core" processors (38). All of the peripheral devices such as counter timers, interrupt controllers, memory controllers, communication functions and etc., are also implemented as soft cores in the FPGA logic blocks.

Using soft-core processors in an FPGA based MPSoC architecture has numerous advantages. Soft core processors can be instantiated as many times as the designer requires as long as there are enough FPGA resources available. Higher levels of overall application performance can be readily achieved by instantiating multiple soft-core processors. Moreover, when soft-core processors are used in the architecture of an MPSoC, their hardware features can be customized according to the requirements of the application. For example an FPGA designer can customize his/her soft-core processor configuration by sizing, including or excluding certain features of the processor according to the performance needs of the application. Soft-core

processors support generation-time configuration options to allow designers to trade off performance and cost. Examples of generation-time configuration options include pipeline implementation, cache size, multiplier implementation, divider implementation, barrel shifter implementation, and tightly coupled memories etc. The designer can include or exclude these features at generation time and thus optimize the architecture. A soft-core processor can also be complemented by a hardware accelerators configured out of the FPGA logic blocks.

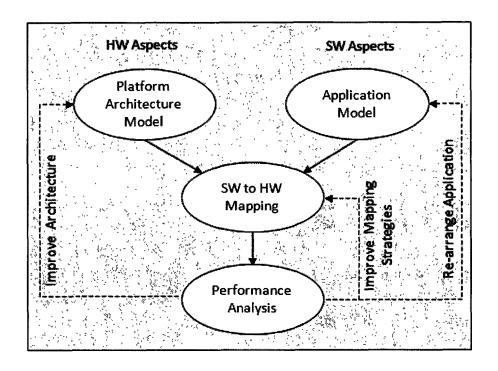

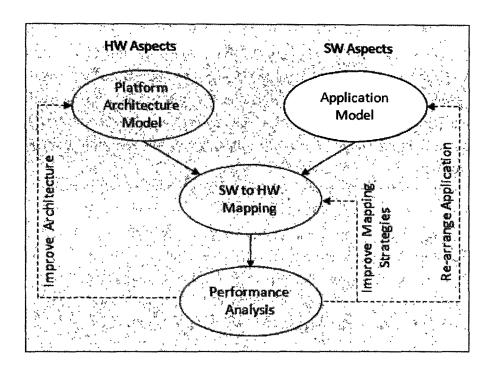

# 6. The Hardware / Software Co-design Flow

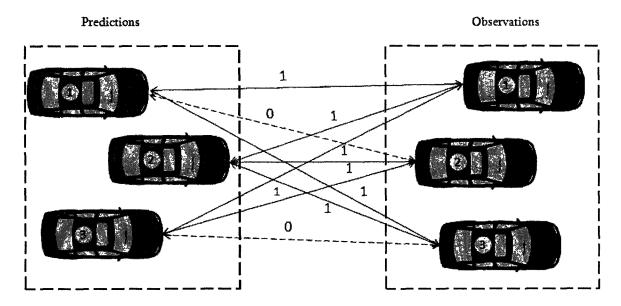

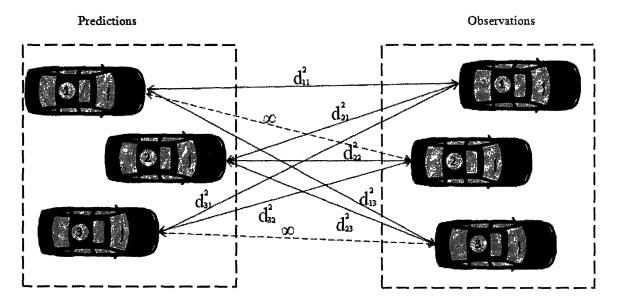

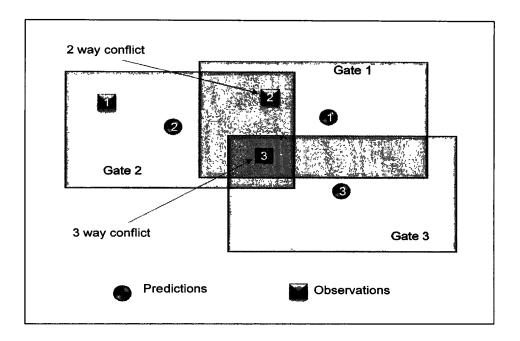

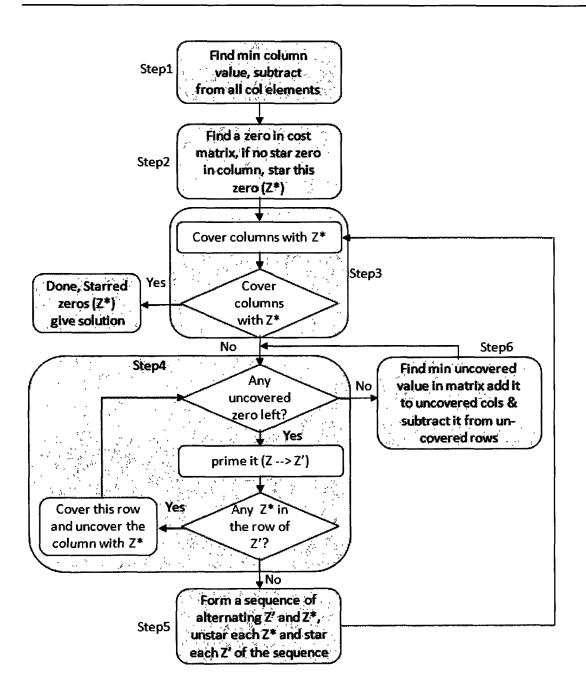

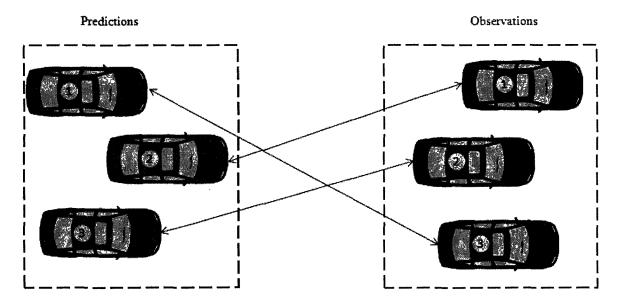

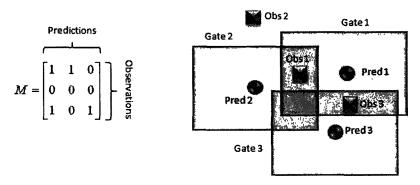

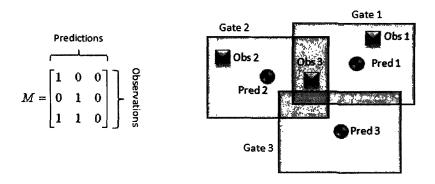

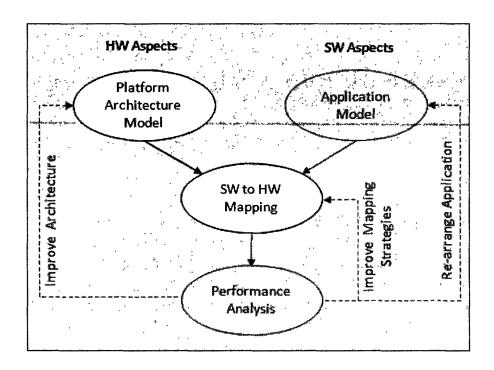

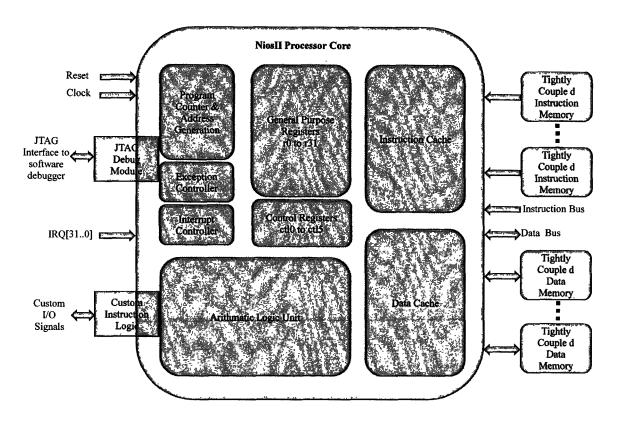

We follow the Y-chart hardware/software co-design flow (43) for the design of our MTT implementation in FPGA based MPSoC. The Y-chart co-design flow is illustrated in Figure 14. According to the Y-chart approach, an application model, derived from a target application domain, describes the functional behavior of an application in an architecture-independent manner.